www.ti.com

UART Registers

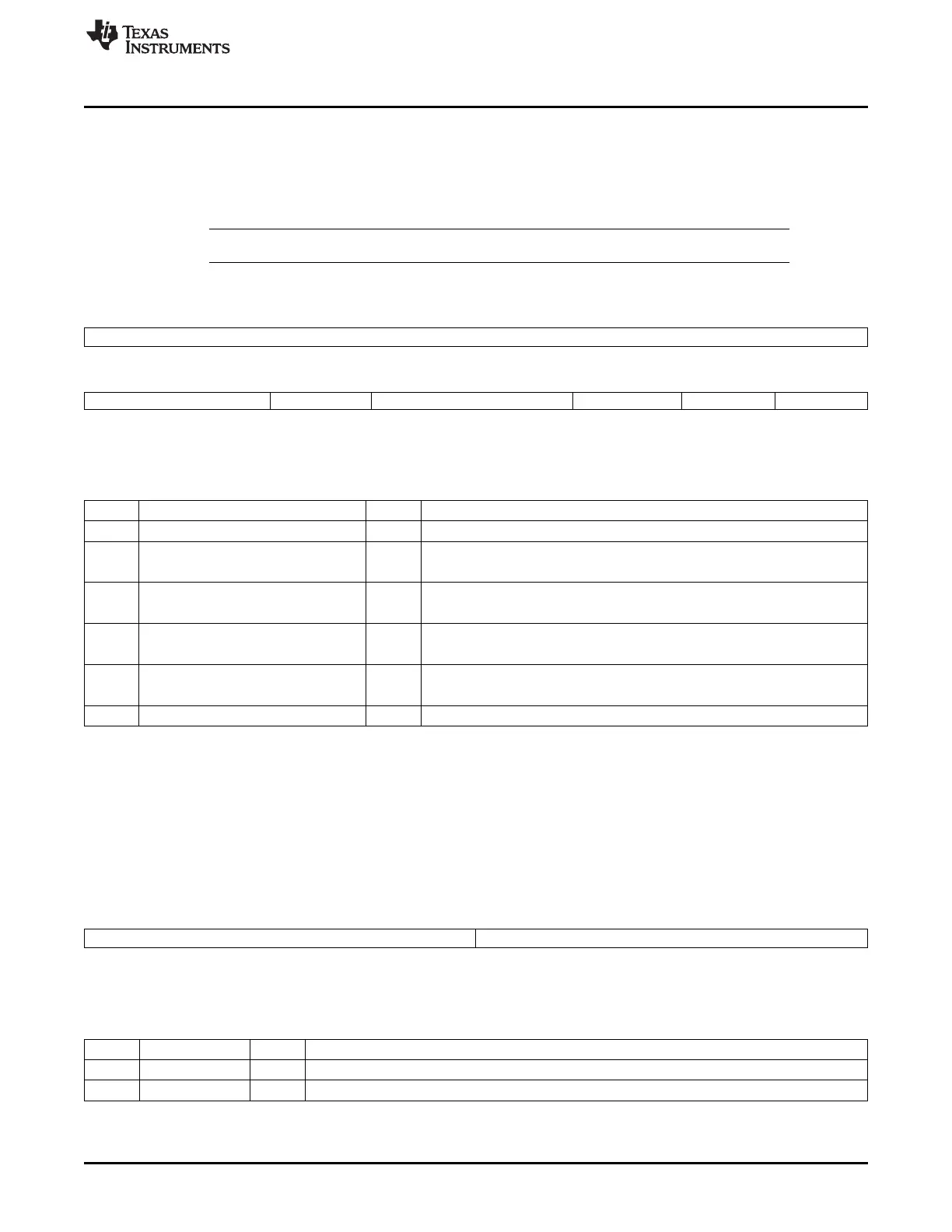

19.5.1.21 Status FIFO Line Status Register (SFLSR)

Reading the status FIFO line status register (SFLSR) effectively reads frame status information from the

status FIFO. This register does not physically exist. Reading this register increments the status FIFO read

pointer (SFREGL and SFREGH must be read first). The status FIFO line status register (SFLSR) is shown

in Figure 19-54 and described in Table 19-52.

NOTE: Top of RX FIFO = Next frame to be read from RX FIFO.

Figure 19-54. Status FIFO Line Status Register (SFLSR)

15 8

Reserved

R-0

7 5 4 3 2 1 0

Reserved OE_ERROR FRAME_TOO_LONG_ERROR ABORT_DETECT CRC_ERROR Reserved

R-0 R-unknown R-unknown R-unknown R-unknown R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 19-52. Status FIFO Line Status Register (SFLSR) Field Descriptions

Bit Field Value Description

15-5 Reserved 0 Reserved.

4 OE_ERROR 0 No error

1 Overrun error in RX FIFO when frame at top of RX FIFO was received.

3 FRAME_TOO_LONG_ERROR 0 No error

1 Frame-length too long error in frame at top of RX FIFO.

2 ABORT_DETECT 0 No error

1 Abort pattern detected in frame at top of RX FIFO.

1 CRC_ERROR 0 No error

1 CRC error in frame at top of RX FIFO.

0 Reserved 0 Reserved.

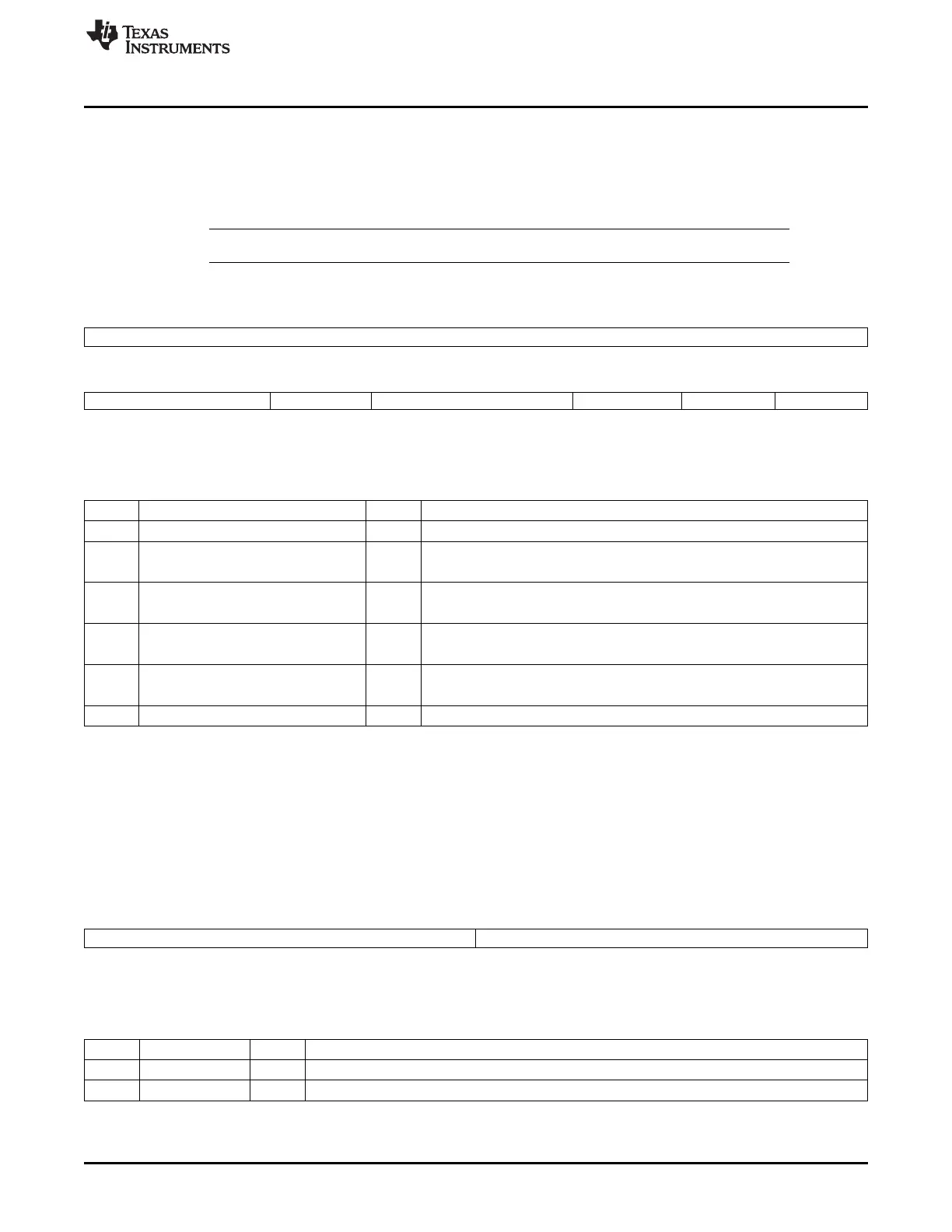

19.5.1.22 RESUME Register

The RESUME register is used to clear internal flags, which halt transmission/reception when an

underrun/overrun error occurs. Reading this register resumes the halted operation. This register does not

physically exist and always reads as 00. The RESUME register is shown in Figure 19-55 and described in

Table 19-53.

Figure 19-55. RESUME Register

15 8 7 0

Reserved RESUME

R-0 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 19-53. RESUME Register Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7-0 RESUME 0-FFh Dummy read to restart the TX or RX.

3525

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...