www.ti.com

Enhanced Capture (eCAP) Module

15.3.4.1.9 ECEINT Register (offset = 2Ch) [reset = 0h]

ECEINT is shown in Figure 15-124 and described in Table 15-117.

The interrupt enable bits (CEVTn) block any of the selected events from generating an interrupt. Events

will still be latched into the flag bit (ECFLG register) and can be forced or cleared via the ECFRC and

ECCLR registers. The proper procedure for configuring peripheral modes and interrupts is: 1. Disable

global interrupts. 2. Stop eCAP counter. 3. Disable eCAP interrupts. 4. Configure peripheral registers. 5.

Clear spurious eCAP interrupt flags. 6. Enable eCAP interrupts. 7. Start eCAP counter. 8. Enable global

interrupts.

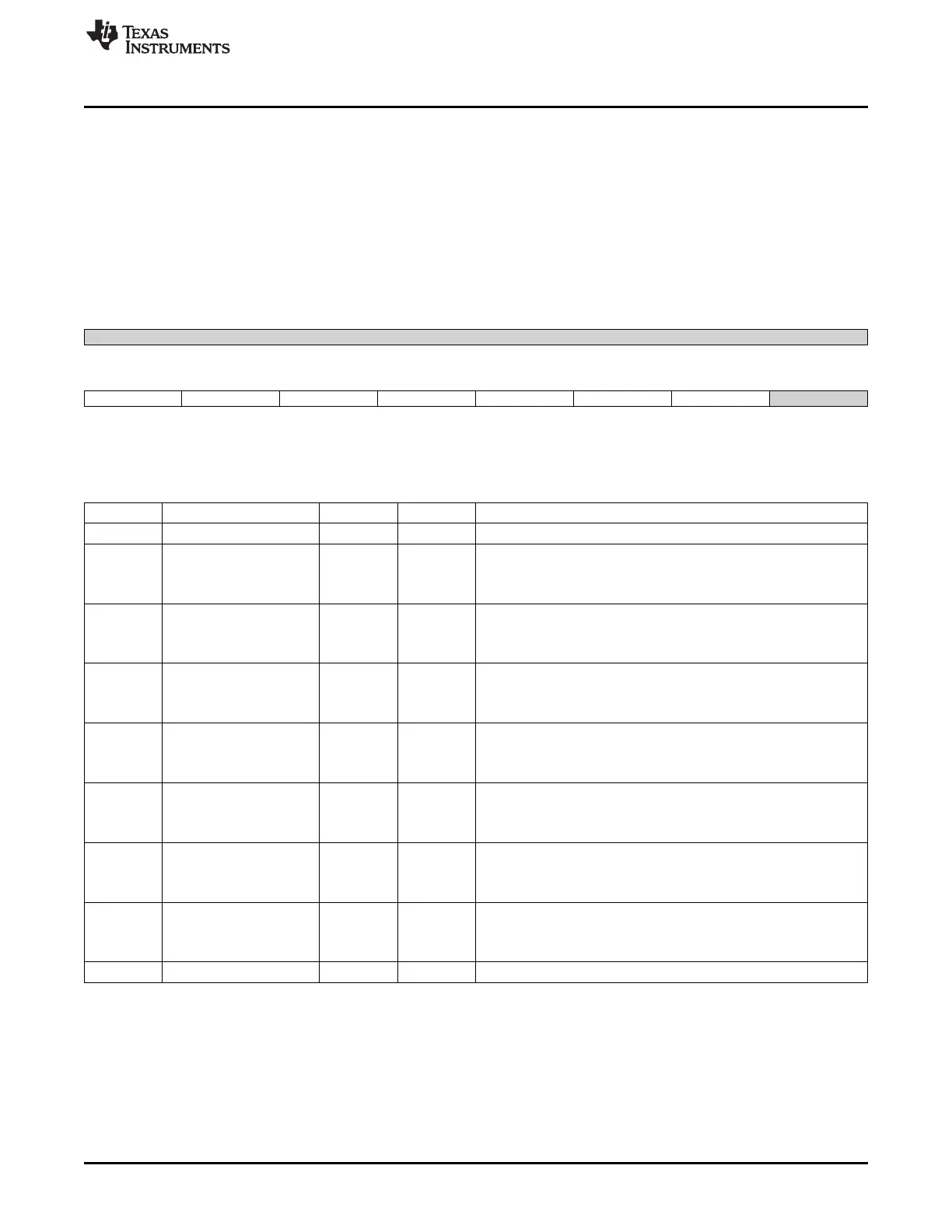

Figure 15-124. ECEINT Register

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

CMPEQ PRDEQ CNTOVF CEVT4 CEVT3 CEVT2 CEVT1 Reserved

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

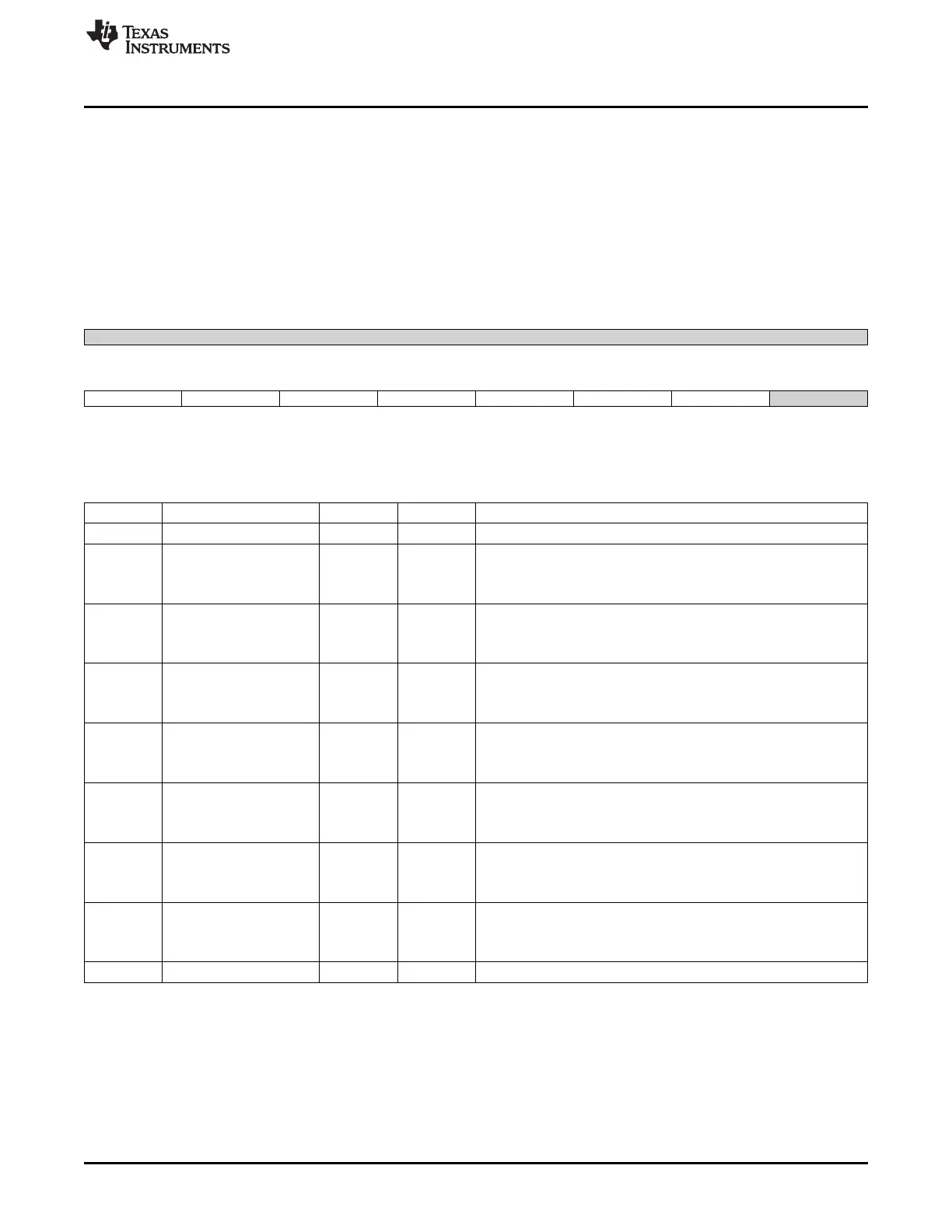

Table 15-117. ECEINT Register Field Descriptions

Bit Field Type Reset Description

15-8 Reserved R 0h

7 CMPEQ R/W 0h

Counter Equal Compare Interrupt Enable.

0x0 = Disable Compare Equal as an Interrupt source.

0x1 = Enable Compare Equal as an Interrupt source.

6 PRDEQ R/W 0h

Counter Equal Period Interrupt Enable.

0x0 = Disable Period Equal as an Interrupt source.

0x1 = Enable Period Equal as an Interrupt source.

5 CNTOVF R/W 0h

Counter Overflow Interrupt Enable.

0x0 = Disable counter Overflow as an Interrupt source.

0x1 = Enable counter Overflow as an Interrupt source.

4 CEVT4 R/W 0h

Capture Event 4 Interrupt Enable.

0x0 = Disable Capture Event 4 as an Interrupt source.

0x1 = Enable Capture Event 4 as an Interrupt source.

3 CEVT3 R/W 0h

Capture Event 3 Interrupt Enable.

0x0 = Disable Capture Event 3 as an Interrupt source.

0x1 = Enable Capture Event 3 as an Interrupt source.

2 CEVT2 R/W 0h

Capture Event 2 Interrupt Enable.

0x0 = Disable Capture Event 2 as an Interrupt source.

0x1 = Enable Capture Event 2 as an Interrupt source.

1 CEVT1 R/W 0h

Capture Event 1 Interrupt Enable .

0x0 = Disable Capture Event 1 as an Interrupt source.

0x1 = Enable Capture Event 1 as an Interrupt source.

0 Reserved R 0h

1645

SPRUH73H–October 2011–Revised April 2013 Pulse-Width Modulation Subsystem (PWMSS)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...