Array0 Array1 Array2 Array3

Eacharraysubmit

asoneTR

Array0 Array3Array1 Array2

(SRC|DST)

BIDX

(SRC|DST)

BIDX

(SRC|DST)

BIDX

(SRC|DST)

BIDX

(SRC|DST)

BIDX

(SRC|DST)

BIDX

(SRC|DST)

BIDX

Array0

Array3

(SRC|DST)

Array1

BIDX BIDX

(SRC|DST)

Array2

Frame0

Frame1

Frame2

(SRC|DST)

CIDX

(SRC|DST)

CIDX

AB_Synctransfer

www.ti.com

Functional Description

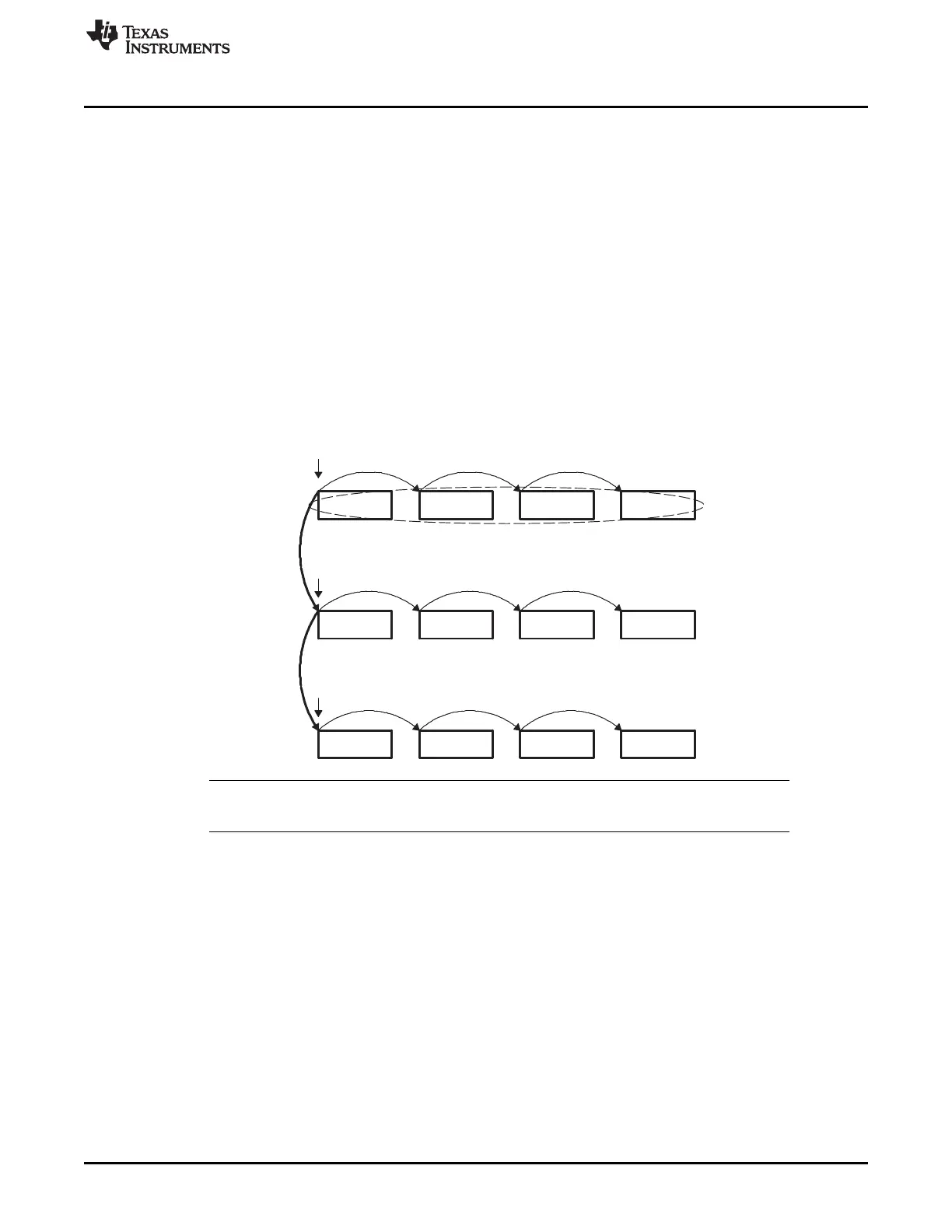

11.3.2.2 AB-Synchronized Transfers

In a AB-synchronized transfer, each EDMA3 sync event initiates the transfer of 2 dimensions or one

frame. In other words, each event/TR packet conveys information for one entire frame of BCNT arrays of

ACNT bytes. Thus, CCNT events are needed to completely service a PaRAM set.

Arrays are always separated by SRCBIDX and DSTBIDX as shown in Figure 11-8. Frames are always

separated by SRCCIDX and DSTCIDX.

Note that for AB-synchronized transfers, after a TR for the frame is submitted, the address update is to

add SRCCIDX/DSTCIDX to the beginning address of the beginning array in the frame. This is different

from A-synchronized transfers where the address is updated by adding SRCCIDX/DSTCIDX to the start

address of the last array in the frame. See Section 11.3.3.6 for details on parameter set updates.

Figure 11-8 shows an AB-synchronized transfer of 3 (CCNT) frames of 4 (BCNT) arrays of n (ACNT)

bytes. In this example, a total of 3 sync events (CCNT) exhaust a PaRAM set; that is, a total of 3 transfers

of 4 arrays each completes the transfer.

Figure 11-8. AB-Synchronized Transfers (ACNT = n, BCNT = 4, CCNT = 3)

NOTE: ABC-synchronized transfers are not directly supported. But can be logically achieved by

chaining between multiple AB-synchronized transfers.

11.3.3 Parameter RAM (PaRAM)

The EDMA3 controller is a RAM-based architecture. The transfer context (source/destination addresses,

count, indexes, etc.) for DMA or QDMA channels is programmed in a parameter RAM table within

EDMA3CC, referred to as PaRAM. The PaRAM table is segmented into multiple PaRAM sets. Each

PaRAM set includes eight four-byte PaRAM set entries (32-bytes total per PaRAM set), which includes

typical DMA transfer parameters such as source address, destination address, transfer counts, indexes,

options, etc.

The PaRAM structure supports flexible ping-pong, circular buffering, channel chaining, and auto-reloading

(linking).

The contents of the PaRAM include the following:

• 256 PaRAM sets

• 64 channels that are direct mapped and can be used as link or QDMA sets if not used for DMA

channels

• 64 channels remain for link or QDMA sets

881

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...