Userwrite

TR

SrcBuffer

DstBuffer

Submission

PaRAM

EDMA3CC

EDMA3TC0

PRIVID=0,

PRIV=0

Memory

Protection

Attribute

Memory

Protection

Attribute

L2Page

9F0000h

L1DPage

F07800h

CPU

fromuser

Privilegelevel

PRIVID=0

PaRAM

entry5

PRIVID=0,

PRIV=0

Readreq

PRIVID=0,

PRIV=0

Read

Write

Access

allowed

AID0=1

UW=1

AID0=1

UR=1

Accessallowed

Functional Description

www.ti.com

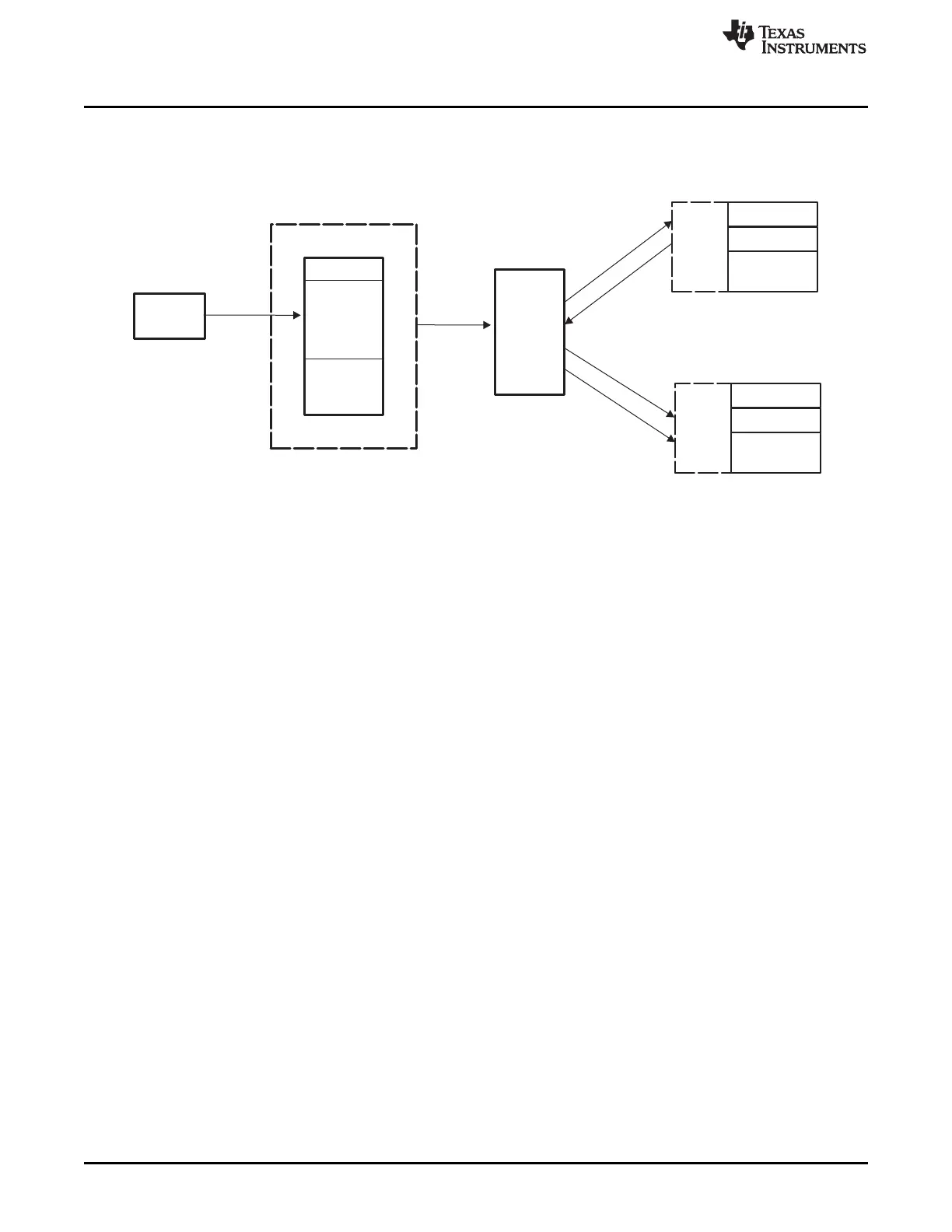

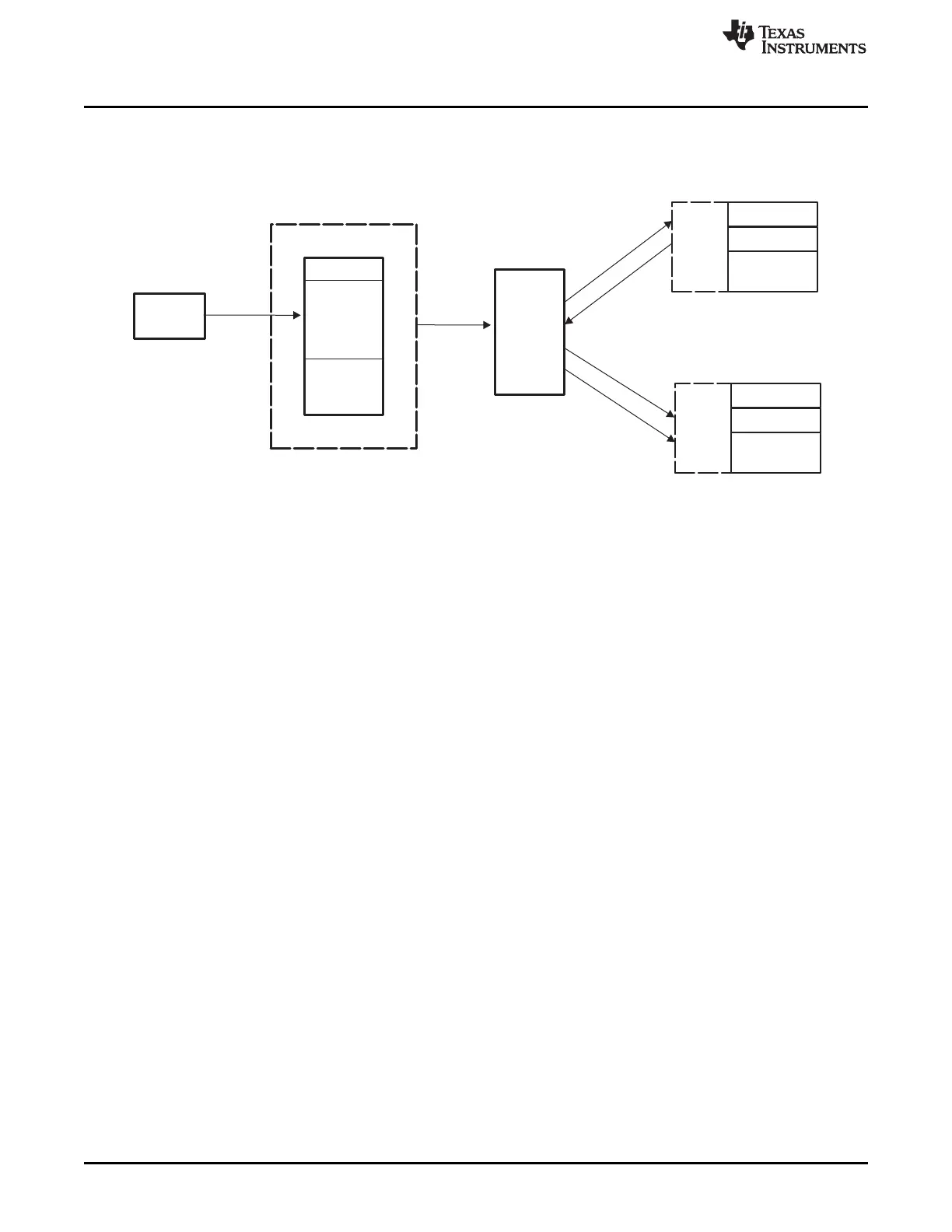

Figure 11-20. Proxy Memory Protection Example

11.3.11 Event Queue(s)

Event queues are a part of the EDMA3 channel controller. Event queues form the interface between the

event detection logic in the EDMA3CC and the transfer request (TR) submission logic of the EDMA3CC.

Each queue is 16 entries deep; thus, each event queue can queue a maximum of 16 events. If there are

more than 16 events, then the events that cannot find a place in the event queue remain set in the

associated event register and the CPU does not stall.

There are four event queues for the device: Queue0, Queue1, Queue2, and Queue3. Events in Queue0

result in submission of its associated transfer requests (TRs) to TC0. Similarly, transfer requests that are

associated with events in Queue3 are submitted to TC3.

An event that wins prioritization against other DMA and/or QDMA pending events is placed at the tail of

the appropriate event queue. Each event queue is serviced in FIFO order. Once the event reaches the

head of its queue and the corresponding transfer controller is ready to receive another TR, the event is

de-queued and the PaRAM set corresponding to the de-queued event is processed and submitted as a

transfer request packet (TRP) to the associated EDMA3 transfer controller.

Queue0 has highest priority and Queue3 has the lowest priority, if Queue0 and Queue1 both have at least

one event entry and if both TC0 and TC1 can accept transfer requests, then the event in Queue0 is de-

queued first and its associated PaRAM set is processed and submitted as a transfer request (TR) to TC0.

See Section 11.3.11.4 for system-level performance considerations. All of the event entries in all of the

event queues are software readable (not writeable) by accessing the event entry registers (Q0E0,

Q0E1,…Q1E15, etc.). Each event entry register characterizes the queued event in terms of the type of

event (manual, event, chained or auto-triggered) and the event number. See Section 11.4.1.4.1 for a

description of the bit fields in the queue event entry registers.

11.3.11.1 DMA/QDMA Channel to Event Queue Mapping

Each of the 64 DMA channels and eight QDMA channels are programmed independently to map to a

specific queue, using the DMA queue number register (DMAQNUM) and the QDMA queue number

register (QDMANUM). The mapping of DMA/QDMA channels is critical to achieving the desired

performance level for the EDMA and most importantly, in meeting real-time deadlines. See

Section 11.3.11.4.

912

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...