0

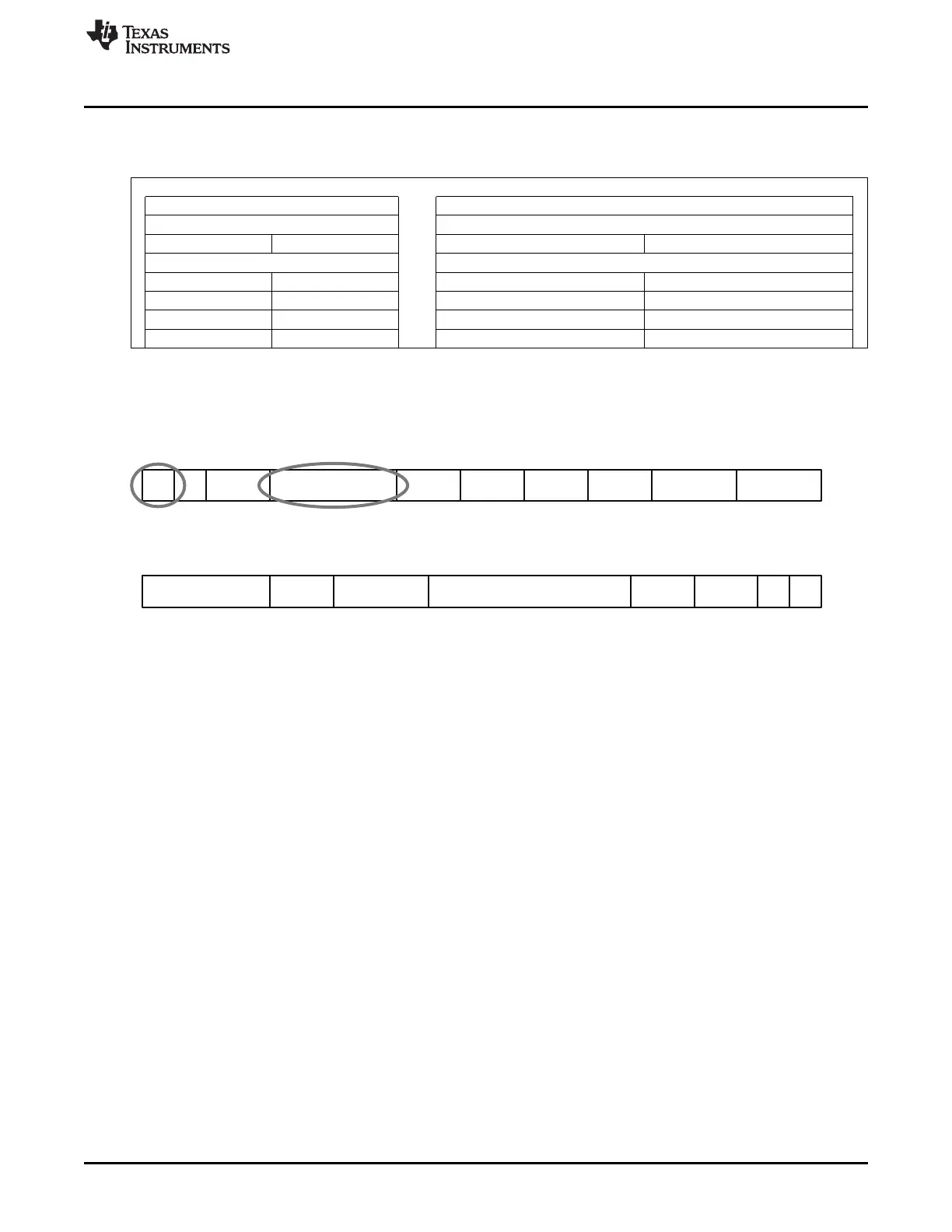

31

0

30

29 28

00

27 24

0000

PRIV Rsvd Rsvd PRIVID ITCCHEN

23

0

TCCHEN

0

22

TCINTENITCINTEN

0

21

1

20

19 18

00

Reserved TCC

00

17 16

15 12

0000

TCC TCCMOD

0

11 10 8

000

FWID SAM

1

0

1

DAM

1

SYNCDIM

1

2

0

STATIC

3

7 4

0000

Reserved

(b)ChannelOptionsParameter(OPT)Content

www.ti.com

Functional Description

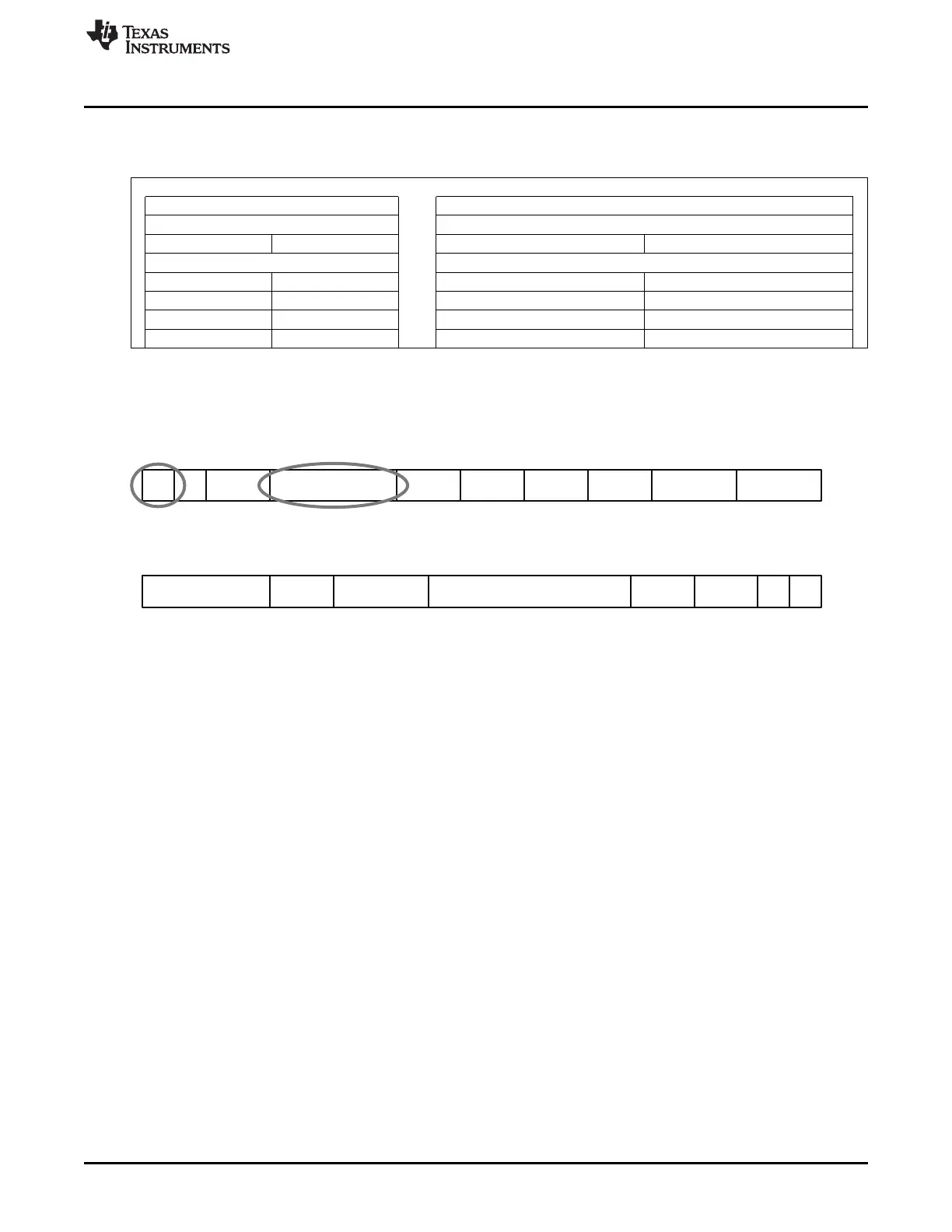

Figure 11-18. PaRAM Set Content for Proxy Memory Protection Example

(a) EDMA3 Parameters

Parameter Contents Parameter

0010 0007h Channel Options Parameter (OPT)

009F 0000h Channel Source Address (SRC)

0001h 0004h Count for 2nd Dimension (BCNT) Count for 1st Dimension (ACNT)

00F0 7800h Channel Destination Address (DST)

0001h 0001h Destination BCNT Index (DSTBIDX) Source BCNT Index (SRCBIDX)

0000h FFFFh BCNT Reload (BCNTRLD) Link Address (LINK)

0001h 1000h Destination CCNT Index (DSTCIDX) Source CCNT Index (SRCCIDX)

0000h 0001h Reserved Count for 3rd Dimension (CCNT)

Figure 11-19. Channel Options Parameter (OPT) Example

The PRIV and PRIVID information travels along with the read and write requests that are issued to the

source and destination memories.

For example, if the access attributes that are associated with the L2 page with the source buffer only allow

supervisor read, write accesses (SR,SW), the user-level read request above is refused. Similarly, if the

access attributes that are associated with the L1D page with the destination buffer only allow supervisor

read and write accesses (SR, SW), the user-level write request above is refused. For the transfer to

succeed, the source and destination pages should have user-read and user-write permissions,

respectively, along with allowing accesses from a PRIVID 0.

Because the programmer's privilege level and privilege identification travel with the read and write

requests, EDMA3 acts as a proxy.

Figure 11-20 illustrates the propagation of PRIV and PRIVID at the boundaries of all the interacting

entities (CPU, EDMA3CC, EDMA3TC, and slave memories).

911

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...