GPMC

www.ti.com

7.1.5.10 GPMC_STATUS

The status register provides global status bits of the GPMC.

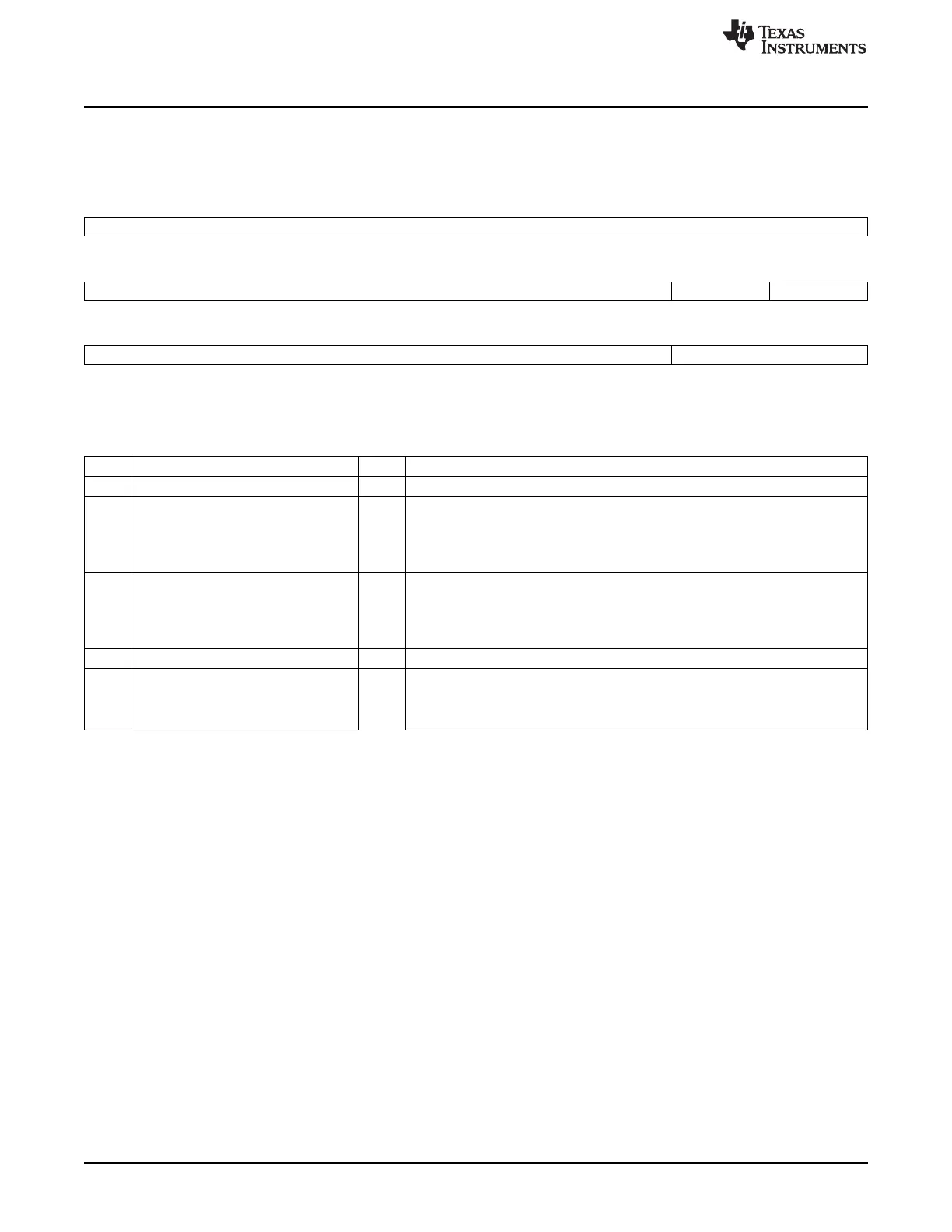

Figure 7-60. GPMC_STATUS

31 16

Reserved

R-0

15 10 9 8

Reserved WAIT1STATUS WAIT0STATUS

R-0 R/W-0 R/W-0

7 1 0

Reserved EMPTYWRITEBUFFERSTATUS

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

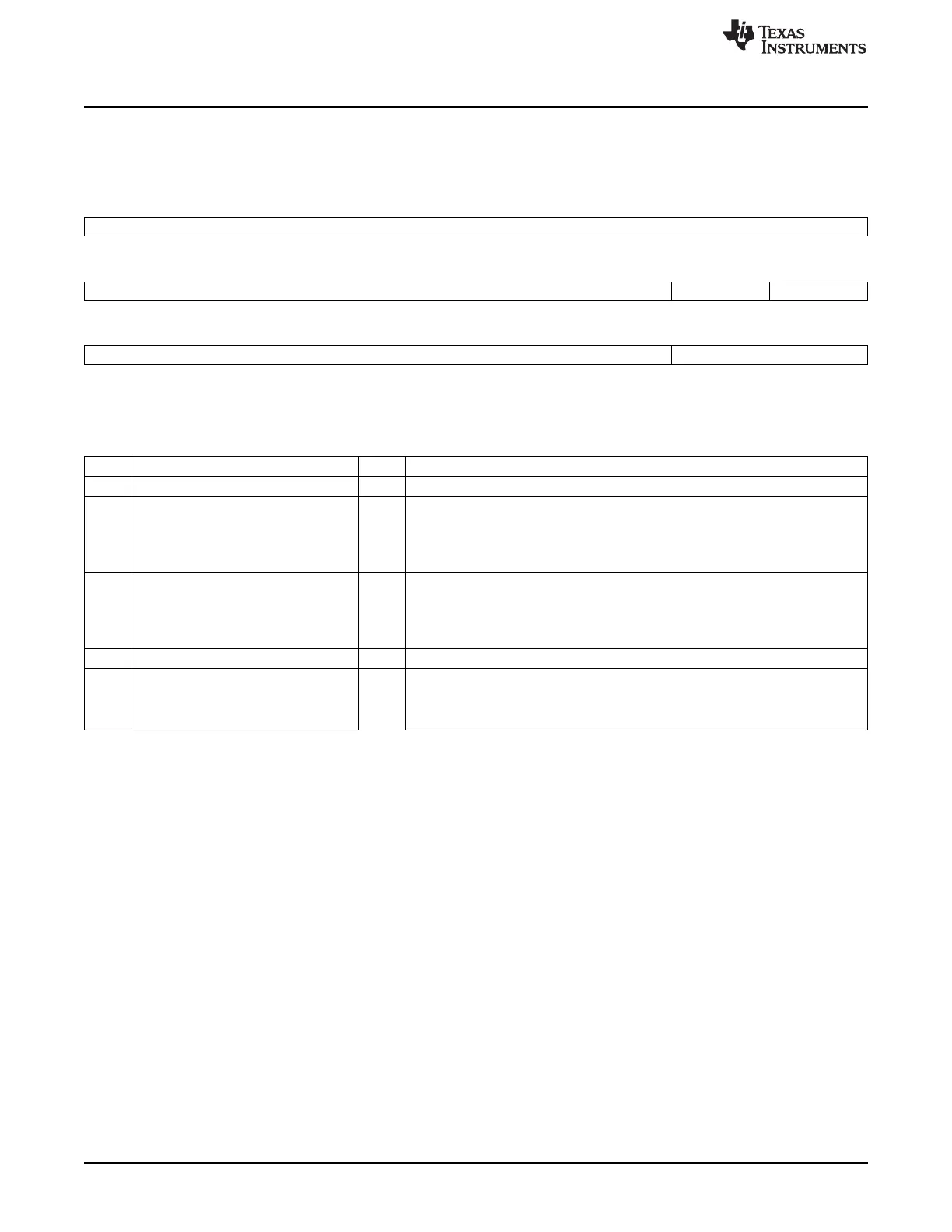

Table 7-64. GPMC_STATUS Field Descriptions

Bit Field Value Description

31-10 Reserved 0 Reserved

9 WAIT1STATUS Is a copy of input pin WAIT1. (Reset value is WAIT1 input pin sampled at IC

reset)

0 WAIT1 asserted (inactive state)

1 WAIT1 de-asserted

8 WAIT0STATUS Is a copy of input pin WAIT0. (Reset value is WAIT0 input pin sampled at IC

reset)

0 WAIT0 asserted (inactive state)

1 WAIT0 de-asserted

7-1 Reserved 0 Reserved

0 EMPTYWRITEBUFFERSTATUS Stores the empty status of the write buffer

0 Write Buffer is not empty

1 Write Buffer is empty

374

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...