UART Registers

www.ti.com

Table 19-69. EFR[3:0] Software Flow Control Options

EFR[3:0]

Bit 3 Bit 2 Bit 1 Bit 0 TX/RX Software Flow Control

0 0 X X No transmit flow control

1 0 X X Transmit XON1, XOFF1

0 1 X X Transmit XON2, XOFF2

1 1 X X Transmit XON1, XON2: XOFF1, XOFF2

(1)

X X 0 0 No receive flow control

X X 1 0 Receiver compares XON1, XOFF1

X X 0 1 Receiver compares XON2, XOFF2

X X 1 1 Receiver compares XON1, XON2: XOFF1, XOFF2

(1)

(1)

The XON1 and XON2 characters or the XOFF1 and XOFF2 characters must be transmitted/received sequentially with

XON1/XOFF1 followed by XON2/XOFF2.

19.5.1.38 XON1/ADDR1 Register

In UART mode, XON1 character; in IrDA mode, ADDR1 address 1. The XON1/ADDR1 register is shown

in Figure 19-71 and described in Table 19-70.

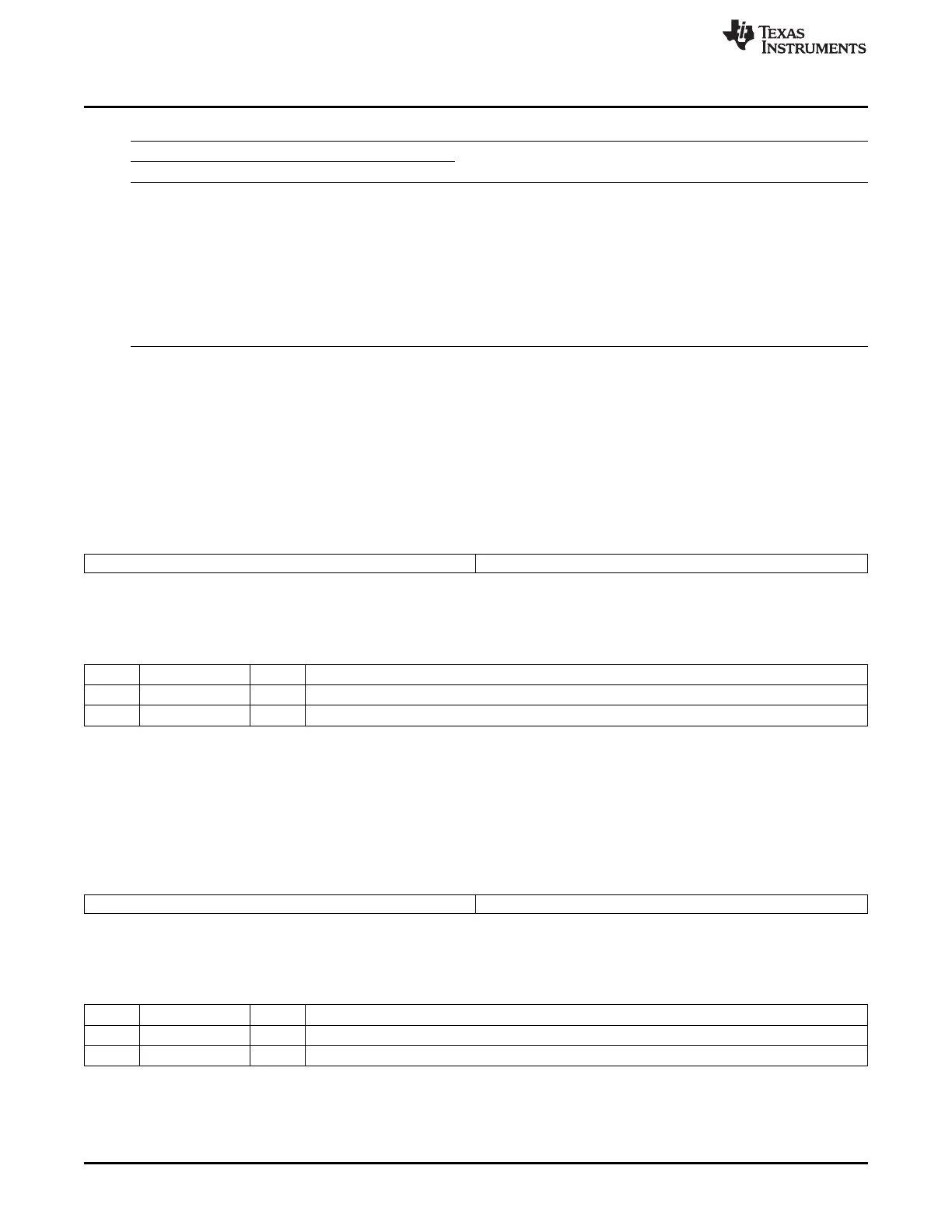

Figure 19-71. XON1/ADDR1 Register

15 8 7 0

Reserved XONWORD1

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 19-70. XON1/ADDR1 Register Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7-0 XONWORD1 0-FFh Stores the 8-bit XON1 character in UART modes and ADDR1 address 1 in IrDA modes.

19.5.1.39 XON2/ADDR2 Register

In UART mode, XON2 character; in IrDA mode, ADDR2 address 2. The XON2/ADDR2 register is shown

in Figure 19-72 and described in Table 19-71.

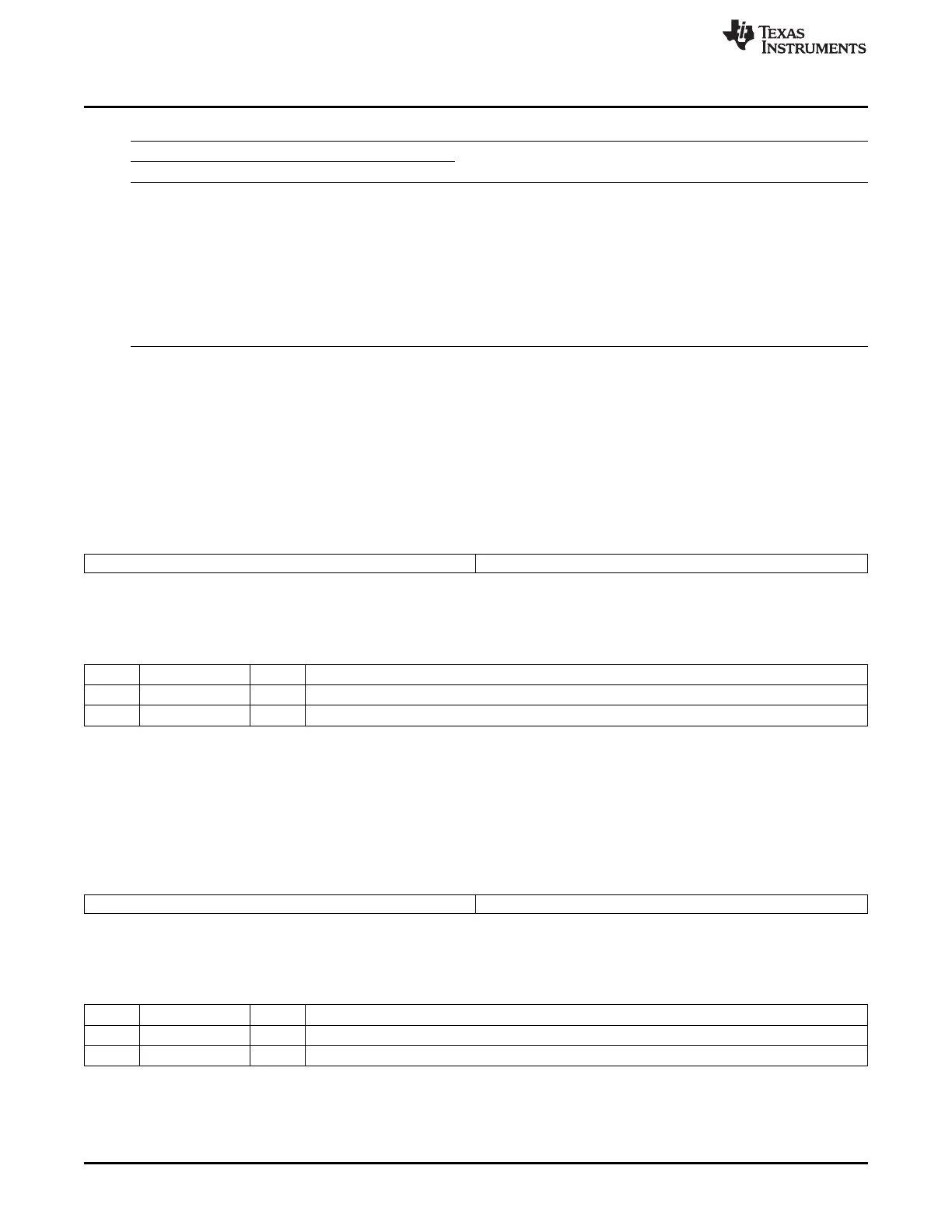

Figure 19-72. XON2/ADDR2 Register

15 8 7 0

Reserved XONWORD2

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 19-71. XON2/ADDR2 Register Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7-0 XONWORD2 0-FFh Stores the 8-bit XON2 character in UART modes and ADDR2 address 2 in IrDA modes.

3538

Universal Asynchronous Receiver/Transmitter (UART) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...