www.ti.com

EDMA3 Registers

11.4.2.7 EDMA3TC Channel Registers

The EDMA3TC channel registers are split into three parts: the programming registers, the source active

registers, and the destination FIFO register. This section describes the registers and their functions. The

program register set is programmed by the channel controller, and is for internal use. The other two sets

are read-only and provided to facilitate advanced debug capabilities. The number of destination FIFO

register sets depends on the destination FIFO depth.

TC0 has a FIFO depth of 2, so there are two sets of destination FIFO registers associated with TC0. TC1,

TC2, and TC3 have a destination FIFO depth of 4, so there are four sets of destination FIFO registers for

each of these transfer controllers.

11.4.2.7.1 Source Active Options Register (SAOPT)

The source active options register (SAOPT) is shown in Figure 11-115 and described in Table 11-100.

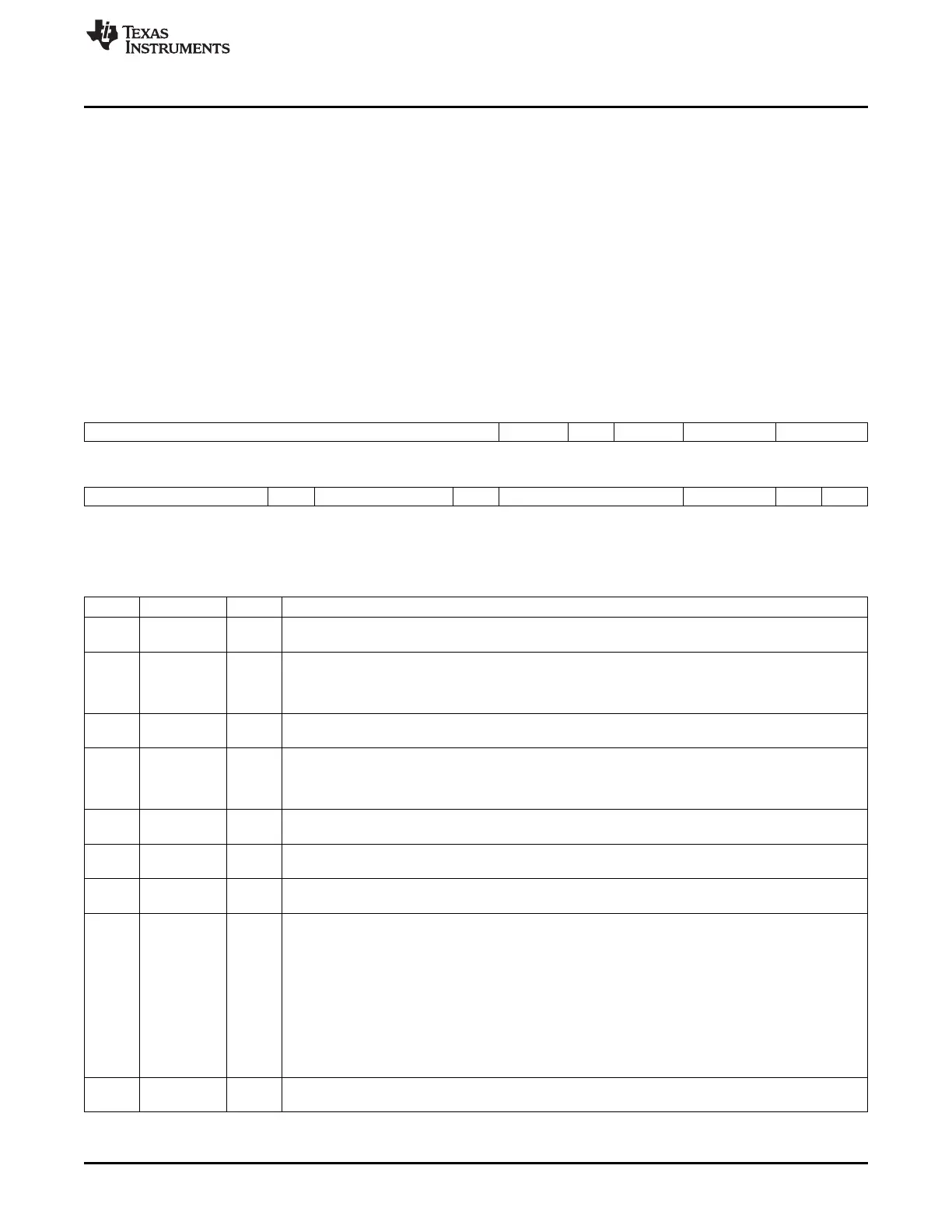

Figure 11-115. Source Active Options Register (SAOPT)

31 23 22 21 20 19 18 17 16

Reserved TCCHEN Rsvd TCINTEN Reserved TCC

R-0 R/W-0 R-0 R/W-0 R-0 R/W-0

15 12 11 10 8 7 6 4 3 2 1 0

TCC Rsvd FWID Rsvd PRI Reserved DAM SAM

R/W-0 R-0 R/W-0 R-0 R/W-0 R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

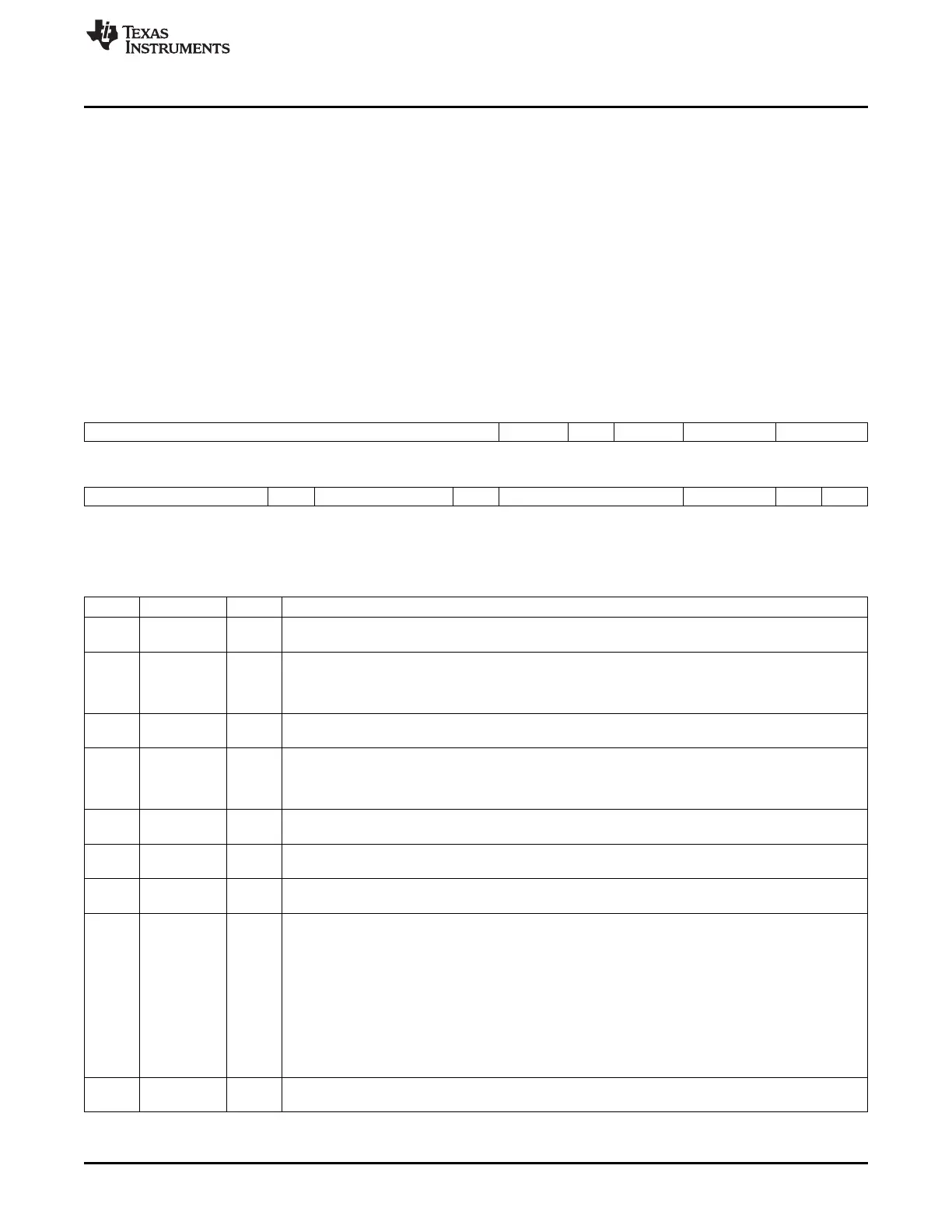

Table 11-100. Source Active Options Register (SAOPT) Field Descriptions

Bit Field Value Description

31-23 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

22 TCCHEN Transfer complete chaining enable

0 Transfer complete chaining is disabled.

1 Transfer complete chaining is enabled.

21 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

20 TCINTEN Transfer complete interrupt enable.

0 Transfer complete interrupt is disabled.

1 Transfer complete interrupt is enabled.

19-18 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

17-12 TCC 0-3Fh Transfer complete code. This 6-bit code is used to set the relevant bit in CER or IPR of the EDMA3PCC

module.

11 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

10-8 FWID 0-7h FIFO width. Applies if either SAM or DAM is set to constant addressing mode.

0 FIFO width is 8-bit.

1h FIFO width is 16-bit.

2h FIFO width is 32-bit.

3h FIFO width is 64-bit.

4h FIFO width is 128-bit.

5h FIFO width is 256-bit.

6h-7h Reserved.

7 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

1005

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...