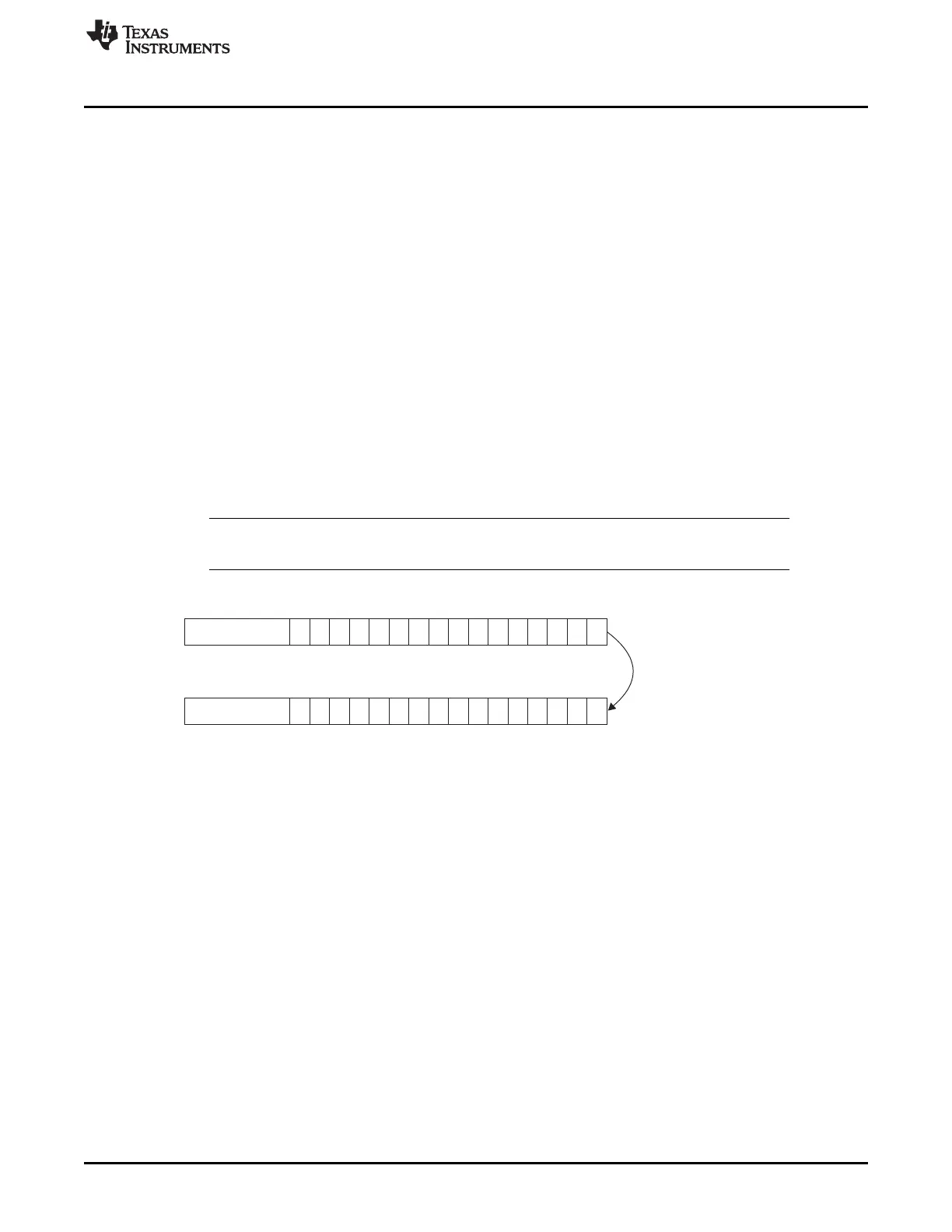

@GPIO_DATAOUT

Register

0

0

0 0 0 0 0 1 0 0 0 0 0 0 0 1

@GPIO_DATAOUT

Register

0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0

Write @GPIO_CLEARDATAOUT

(0000 0000 0000 0001b)

www.ti.com

Functional Description

25.3.4.2.1 Clear Instruction

25.3.4.2.1.1 Clear Interrupt Enable Registers (GPIO_IRQSTATUS_CLR_0 and GPIO_IRQSTATUS_CLR_1):

• A write operation in the clear interrupt enable1 (or enable2) register clears the corresponding bit in the

interrupt enable1 (or enable2) register when the written bit is 1; a written bit at 0 has no effect.

• A read of the clear interrupt enable1 (or enable2) register returns the value of the interrupt enable1 (or

enable2) register.

25.3.4.2.1.2 Clear Data Output Register (GPIO_CLEARDATAOUT):

• A write operation in the clear data output register clears the corresponding bit in the data output

register when the written bit is 1; a written bit at 0 has no effect.

• A read of the clear data output register returns the value of the data output register.

25.3.4.2.1.3 Clear Instruction Example

Assume the data output register (or one of the interrupt enable registers) contains the binary value,

0000 0001 0000 0001h, and you want to clear bit 0.

With the clear instruction feature, write 0000 0000 0000 0001h at the address of the clear data output

register (or at the address of the clear interrupt enable register). After this write operation, a reading of the

data output register (or the interrupt enable register) returns 0000 0001 0000 0000h; bit 0 is cleared.

NOTE: Although the general-purpose interface registers are 32-bits wide, only the 16 least-

significant bits are represented in this example.

Figure 25-4. Write @ GPIO_CLEARDATAOUT Register Example

25.3.4.2.2 Set Instruction

25.3.4.2.2.1 Set Interrupt Enable Registers (GPIO_IRQSTATUS_SET_0 and GPIO_IRQSTATUS_SET_1):

• A write operation in the set interrupt enable1 (or enable2) register sets the corresponding bit in the

interrupt enable1 (or enable2) register when the written bit is 1; a written bit at 0 has no effect.

• A read of the set interrupt enable1 (or enable2) register returns the value of the interrupt enable1 (or

enable2) register.

25.3.4.2.2.2 Set Data Output Register (GPIO_SETDATAOUT):

• A write operation in the set data output register sets the corresponding bit in the data output register

when the written bit is 1; a written bit at 0 has no effect.

• A read of the set data output register returns the value of the data output register.

4065

SPRUH73H–October 2011–Revised April 2013 General-Purpose Input/Output

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...