www.ti.com

DCAN Registers

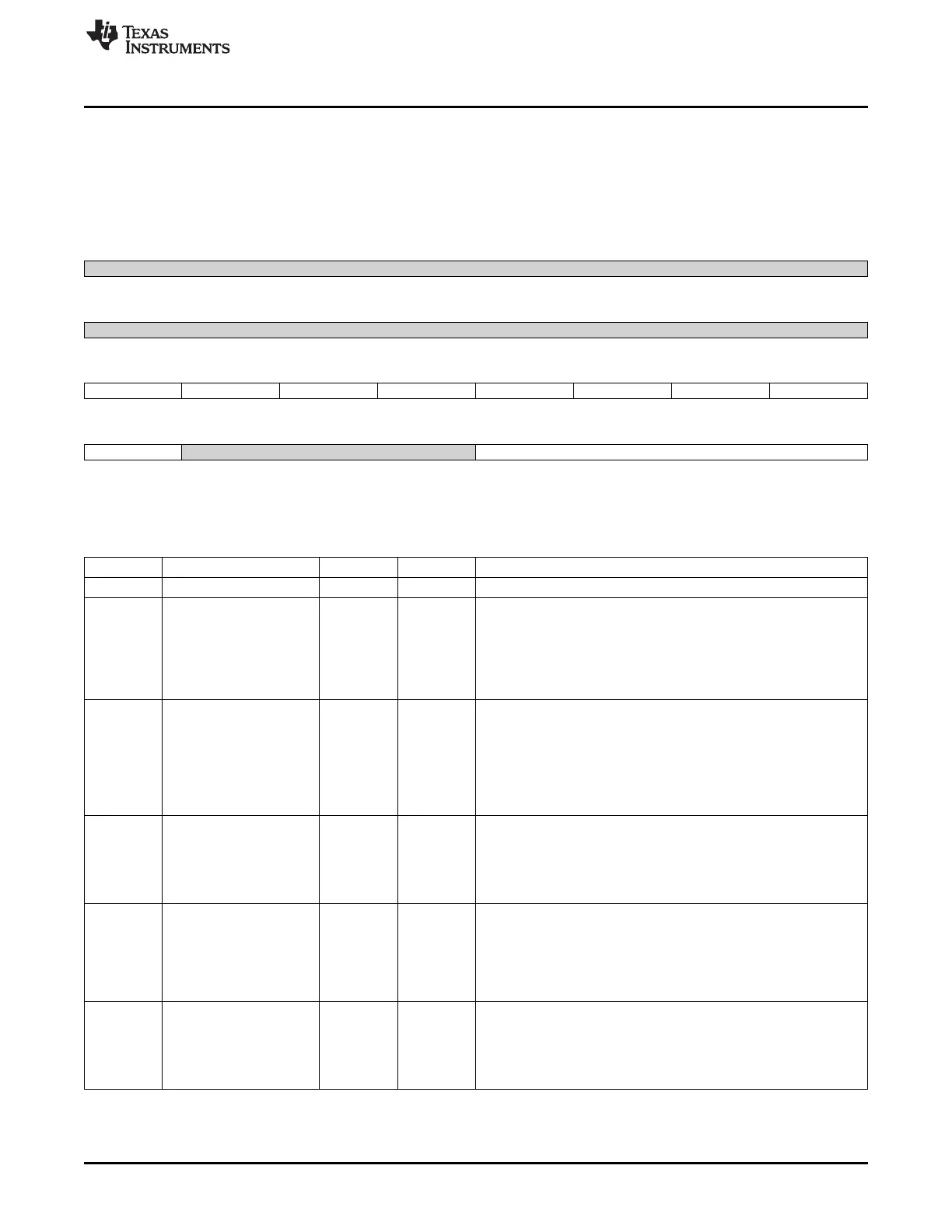

23.4.42 IF2MCTL Register (offset = 12Ch) [reset = 0h]

IF2MCTL is shown in Figure 23-60 and described in Table 23-55.

The bits of the IF2 message control registers mirror the message control bits of a message object. While

Busy bit of IF2 command register is one, IF2 register set is write protected.

Figure 23-60. IF2MCTL Register

31 30 29 28 27 26 25 24

Reserved

R/WP-0h

23 22 21 20 19 18 17 16

Reserved

R/WP-0h

15 14 13 12 11 10 9 8

NewDat MsgLst IntPnd UMask TxIE RxIE RmtEn TxRqst

R/WP-0h R/WP-0h R/WP-0h R/WP-0h R/WP-0h R/WP-0h R/WP-0h R/WP-0h

7 6 5 4 3 2 1 0

EoB Reserved DLC

R/WP-0h R/WP-0h R/WP-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

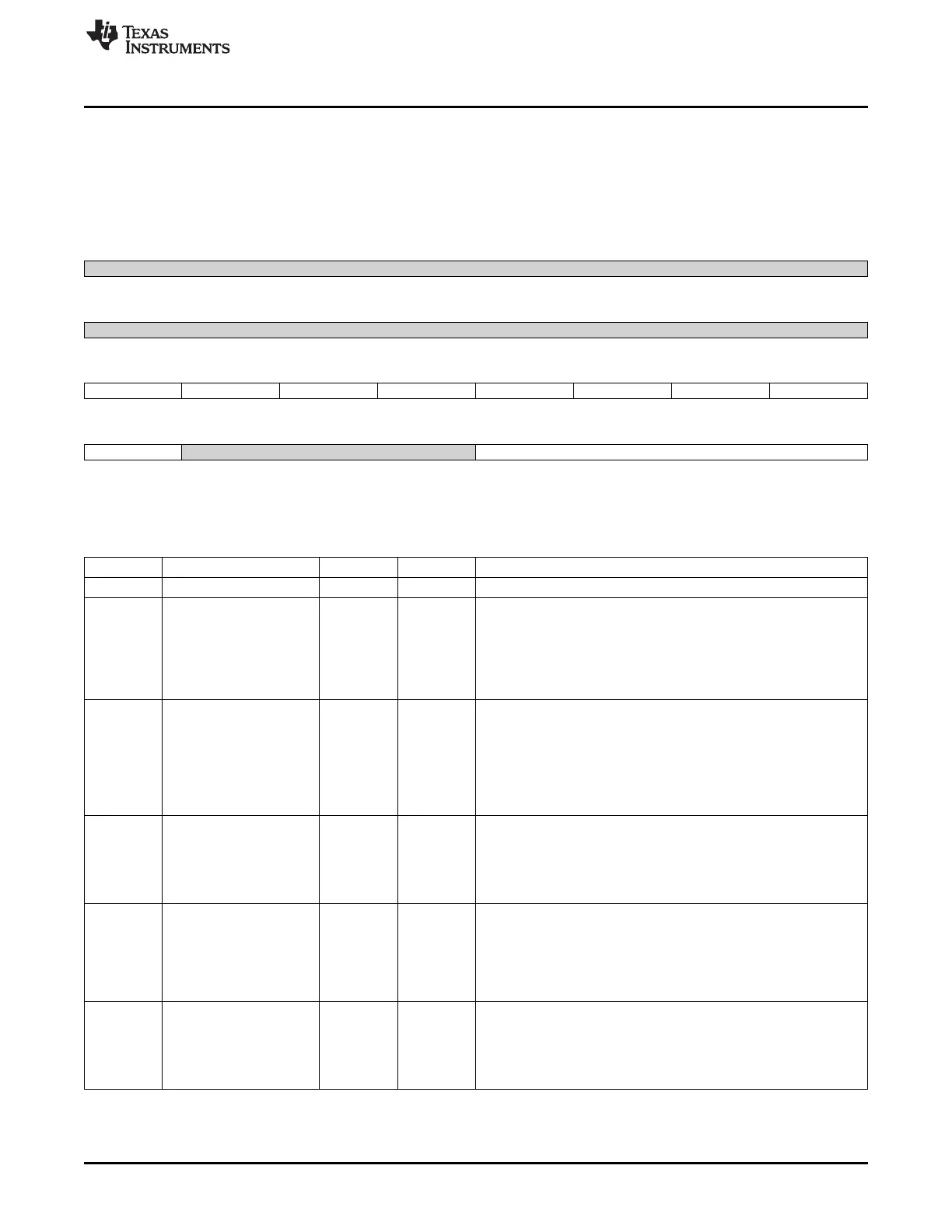

Table 23-55. IF2MCTL Register Field Descriptions

Bit Field Type Reset Description

31-16 Reserved R/WP 0h

15 NewDat R/WP 0h

New data

0x0 = No new data has been written into the data portion of this

message object by the message handler since the last time when

this flag was cleared by the CPU.

0x1 = The message handler or the CPU has written new data into

the data portion of this message object.

14 MsgLst R/WP 0h

Message lost (only valid for message objects with direction =

receive)

0x0 = No message lost since the last time when this bit was reset by

the CPU.

0x1 = The message handler stored a new message into this object

when NewDat was still set, so the previous message has been

overwritten.

13 IntPnd R/WP 0h

Interrupt pending

0x0 = This message object is not the source of an interrupt.

0x1 = This message object is the source of an interrupt. The

Interrupt Identifier in the interrupt register will point to this message

object if there is no other interrupt source with higher priority.

12 UMask R/WP 0h Use acceptance mask.

If the UMask bit is set to one, the message object's mask bits have

to be programmed during initialization of the message object before

MsgVal is set to one.

0x0 = Mask ignored

0x1 = Use mask (Msk[28:0], MXtd, and MDir) for acceptance filtering

11 TxIE R/WP 0h

Transmit interrupt enable

0x0 = IntPnd will not be triggered after the successful transmission of

a frame.

0x1 = IntPnd will be triggered after the successful transmission of a

frame.

3973

SPRUH73H–October 2011–Revised April 2013 Controller Area Network (CAN)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...