UART Registers

www.ti.com

19.5.1.3 Interrupt Enable Register (IER) - UART Mode

The interrupt enable register (IER) can be programmed to enable/disable any interrupt. There are seven

types of interrupt in this mode: receiver error, RHR interrupt, THR interrupt, XOFF received and CTS/RTS

change of state from low to high. Each interrupt can be enabled/disabled individually. There is also a sleep

mode enable bit. The UART interrupt enable register (IER) is shown in Figure 19-36 and described in

Table 19-32.

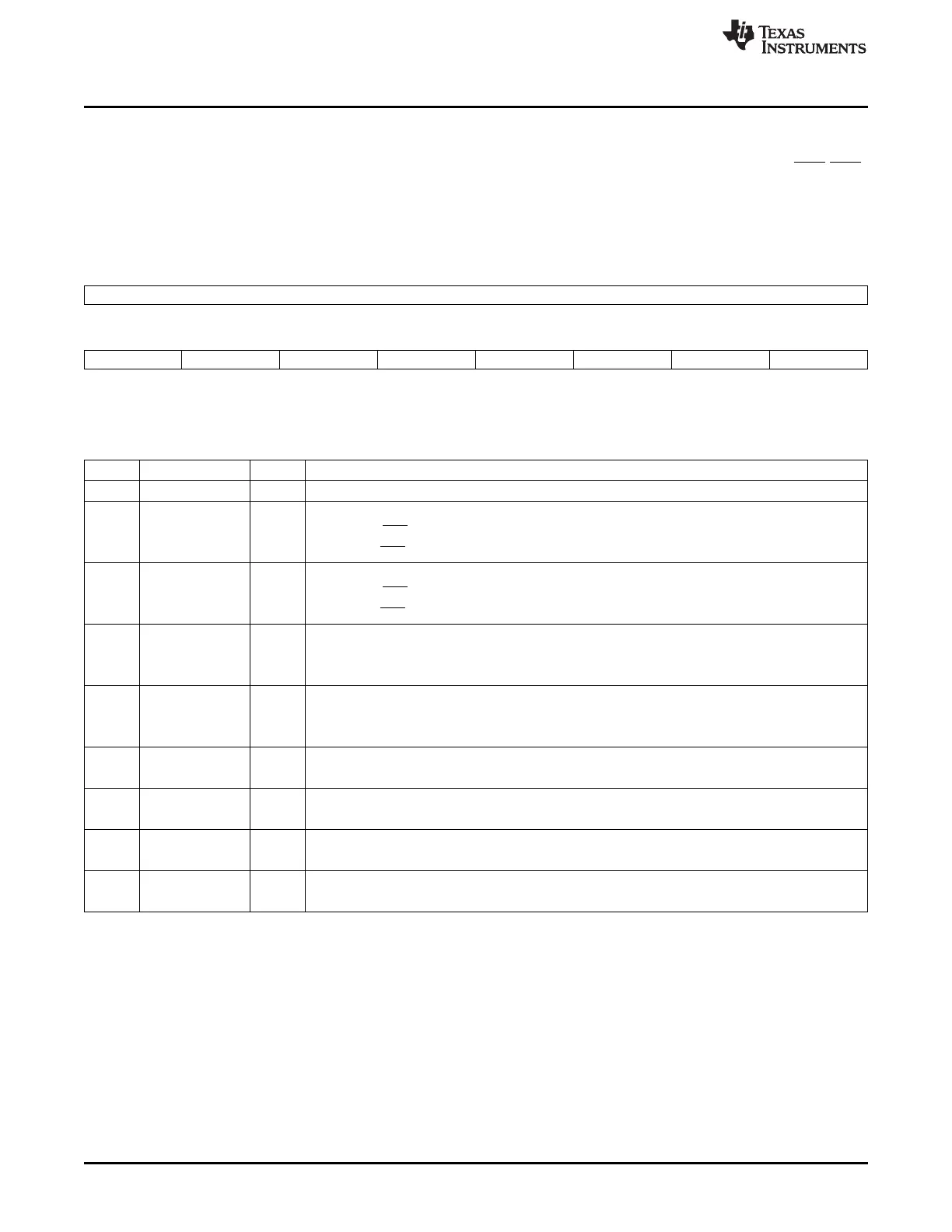

Figure 19-36. UART Interrupt Enable Register (IER)

15 8

Reserved

R-0

7 6 5 4 3 2 1 0

CTSIT RTSIT XOFFIT SLEEPMODE MODEMSTSIT LINESTSIT THRIT RHRIT

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

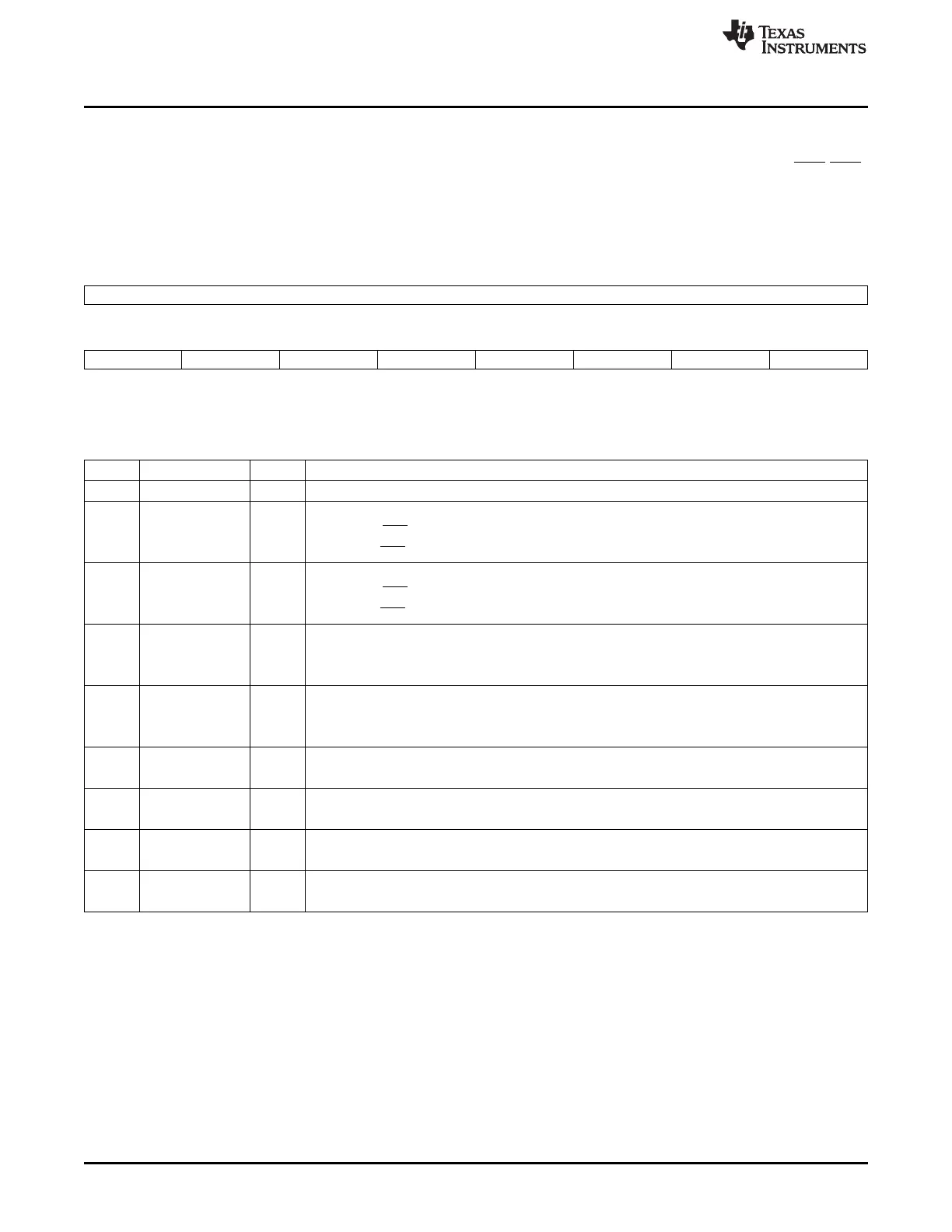

Table 19-32. UART Interrupt Enable Register (IER) Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7 CTSIT Can be written only when EFR[4] = 1.

0 Disables the CTS interrupt.

1 Enables the CTS interrupt.

6 RTSIT Can be written only when EFR[4] = 1.

0 Disables the RTS interrupt.

1 Enables the RTS interrupt.

5 XOFFIT Can be written only when EFR[4] = 1.

0 Disables the XOFF interrupt.

1 Enables the XOFF interrupt.

4 SLEEPMODE Can be only written when EFR[4] = 1.

0 Disables sleep mode.

1 Enables sleep mode (stop baud rate clock when the module is inactive).

3 MODEMSTSIT 0 Disables the modem status register interrupt.

1 Enables the modem status register interrupt

2 LINESTSIT 0 Disables the receiver line status interrupt.

1 Enables the receiver line status interrupt.

1 THRIT 0 Disables the THR interrupt.

1 Enables the THR interrupt.

0 RHRIT 0 Disables the RHR interrupt and time out interrupt.

1 Enables the RHR interrupt and time out interrupt.

3508

Universal Asynchronous Receiver/Transmitter (UART) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...