www.ti.com

Power, Reset, and Clock Management

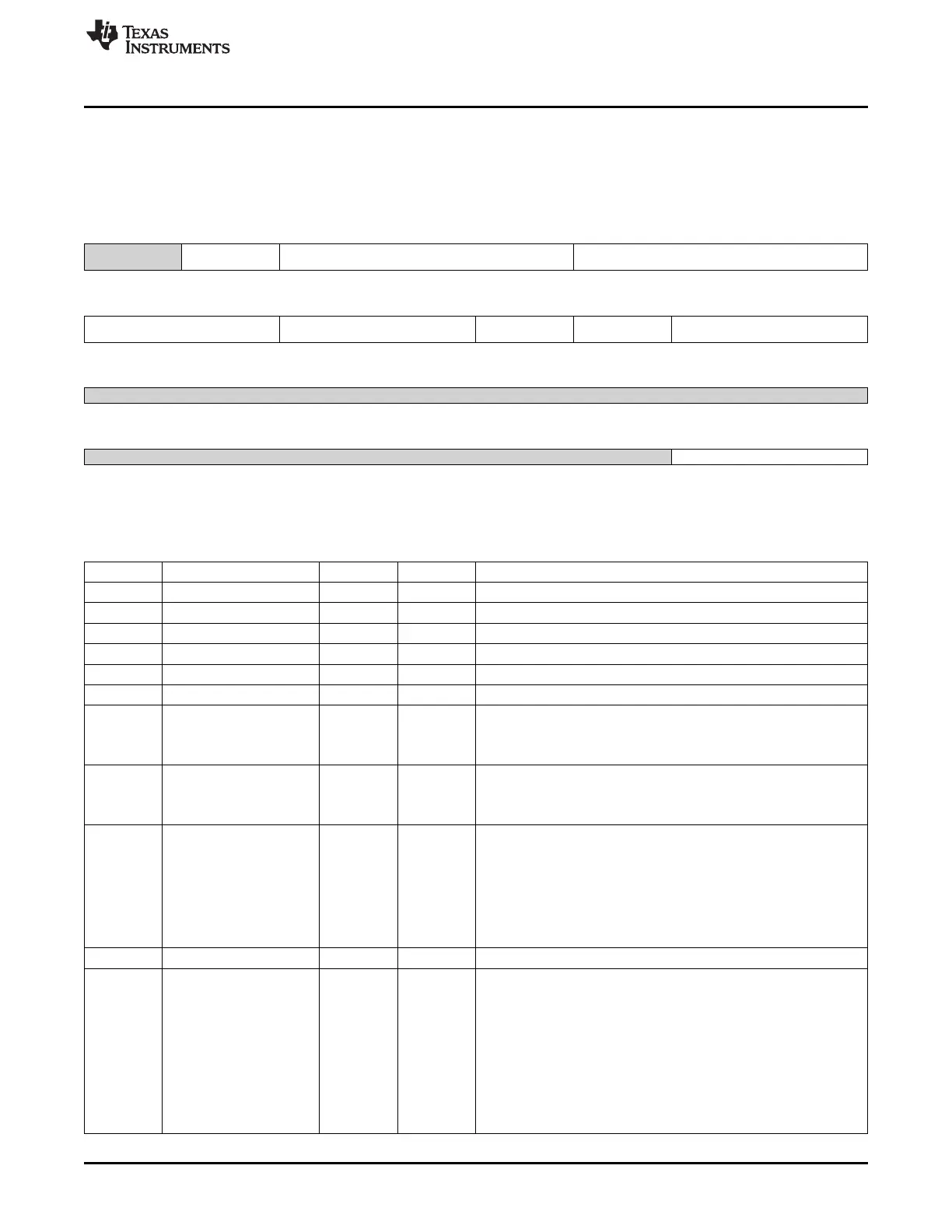

8.1.12.2.6 CM_WKUP_DEBUGSS_CLKCTRL Register (offset = 14h) [reset = 52580002h]

CM_WKUP_DEBUGSS_CLKCTRL is shown in Figure 8-89 and described in Table 8-97.

This register manages the DEBUGSS clocks.

Figure 8-89. CM_WKUP_DEBUGSS_CLKCTRL Register

31 30 29 28 27 26 25 24

Reserved OPTCLK_DEBUG_CL stm_pmd_clkdivsel trc_pmd_clkdivsel

KA

R-0h R/W-1h R/W-2h R/W-2h

23 22 21 20 19 18 17 16

stm_pmd_clksel trc_pmd_clksel OPTFCLKEN_DBGSY STBYST IDLEST

SCLK

R/W-1h R/W-1h R/W-1h R-0h R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved MODULEMODE

R-0h R/W-2h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

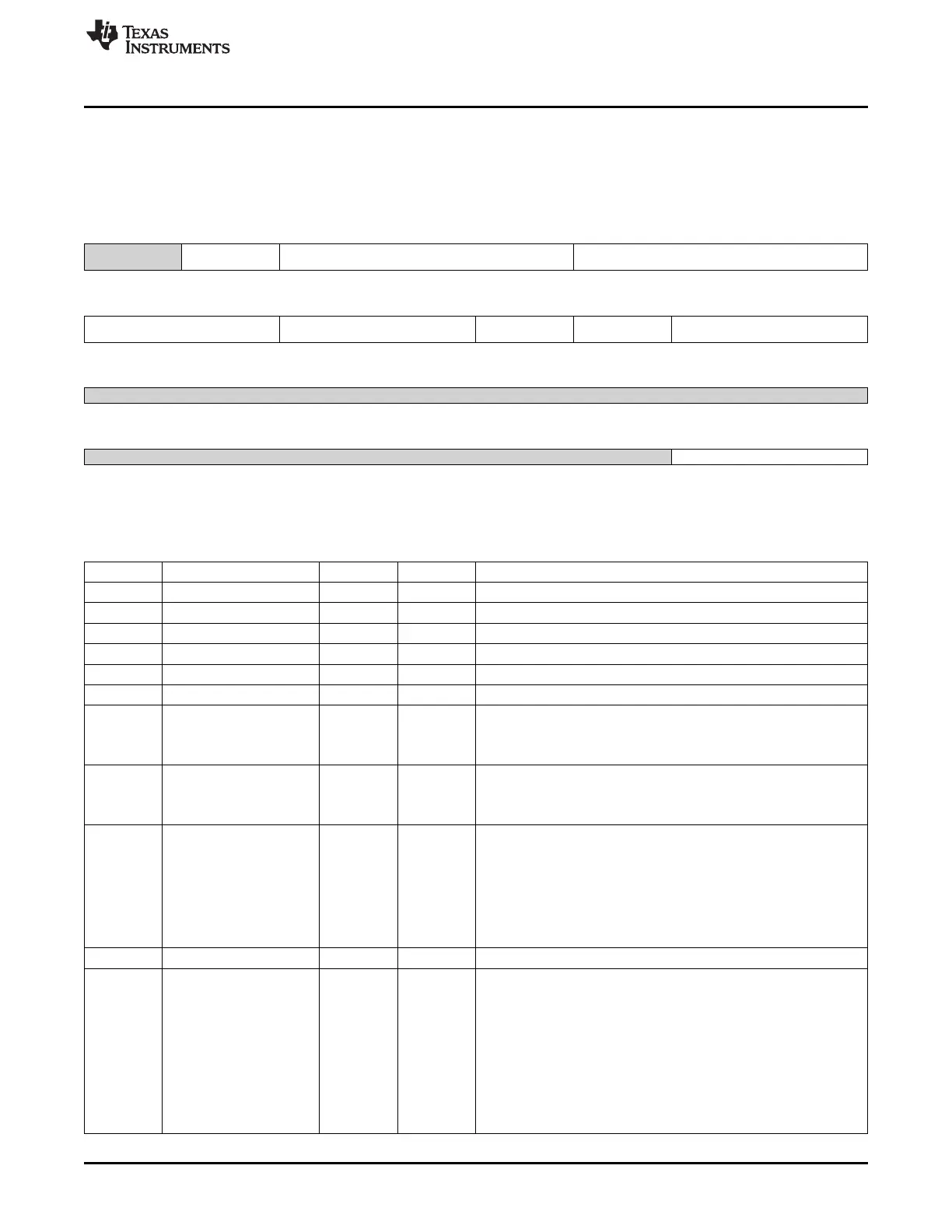

Table 8-97. CM_WKUP_DEBUGSS_CLKCTRL Register Field Descriptions

Bit Field Type Reset Description

31 Reserved R 0h

30 OPTCLK_DEBUG_CLKA R/W 1h

29-27 stm_pmd_clkdivsel R/W 2h

26-24 trc_pmd_clkdivsel R/W 2h

23-22 stm_pmd_clksel R/W 1h

21-20 trc_pmd_clksel R/W 1h

19 OPTFCLKEN_DBGSYSC R/W 1h

Optional functional clock control.

LK

0x0 = FCLK_DIS : Optional functional clock is disabled

0x1 = FCLK_EN : Optional functional clock is enabled

18 STBYST R 0h

Module standby status.

0x0 = Func : Module is functional (not in standby)

0x1 = Standby : Module is in standby

17-16 IDLEST R 0h

Module idle status.

0x0 = Func : Module is fully functional, including OCP

0x1 = Trans : Module is performing transition: wakeup, or sleep, or

sleep abortion

0x2 = Idle : Module is in Idle mode (only OCP part). It is functional if

using separate functional clock

0x3 = Disable : Module is disabled and cannot be accessed

15-2 Reserved R 0h

1-0 MODULEMODE R/W 2h

Control the way mandatory clocks are managed.

0x0 = DISABLED : Module is disable by SW. Any OCP access to

module results in an error, except if resulting from a module wakeup

(asynchronous wakeup).

0x1 = RESERVED_1 : Reserved

0x2 = ENABLE : Module is explicitly enabled. Interface clock (if not

used for functions) may be gated according to the clock domain

state. Functional clocks are guarantied to stay present. As long as in

this configuration, power domain sleep transition cannot happen.

0x3 = RESERVED : Reserved

621

SPRUH73H–October 2011–Revised April 2013 Power, Reset, and Clock Management (PRCM)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...