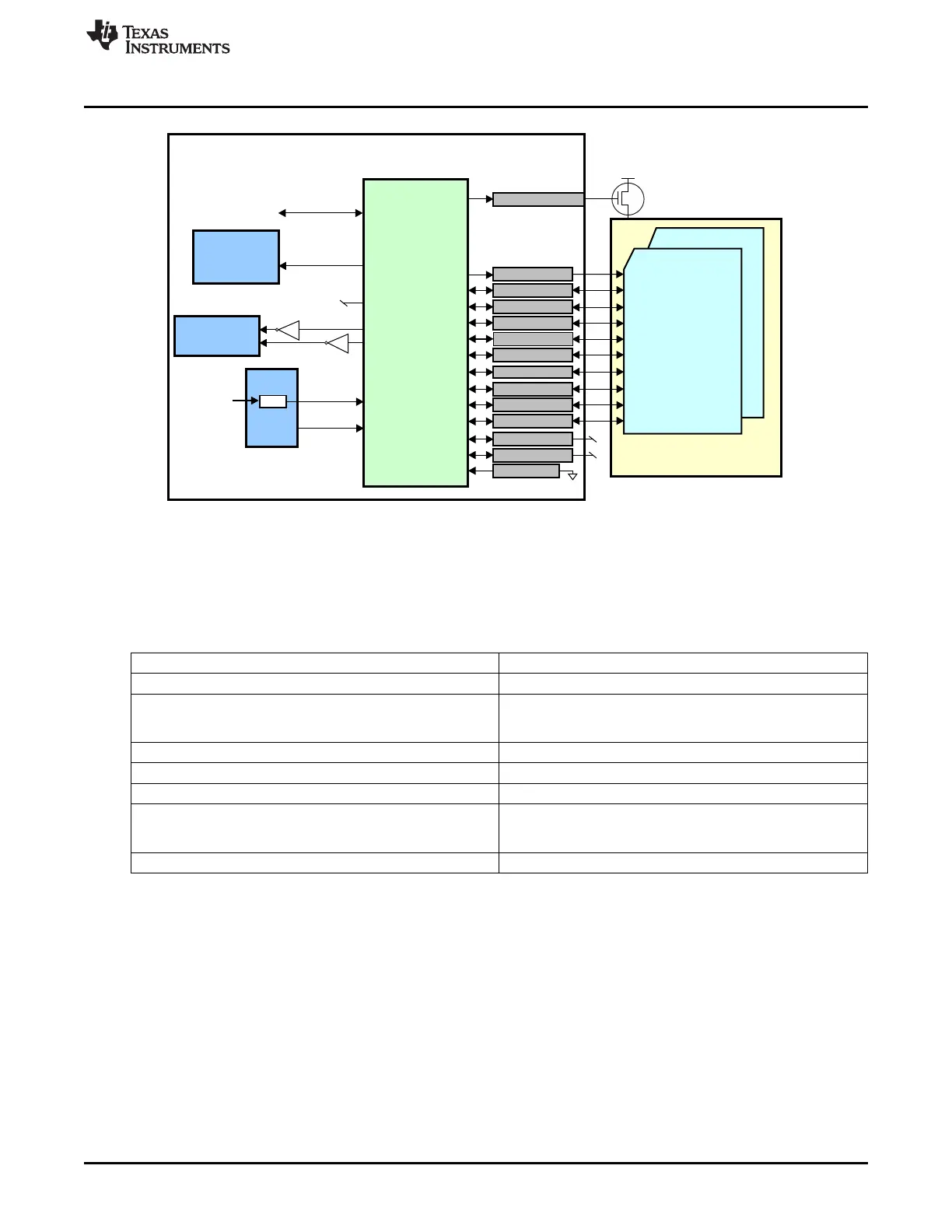

MMC Cards

(8 bit)

CLK

DATA0

Connector VDD Plane

CMD

DATA1

DATA2

DATA3

MMCHS

Controller

L4 Peripheral

Interconnect

MMC/SD I/F

Pads

MPU

Subsystem

EDMA

SINTERRUPTN

SDMARREQN

SDMAWREQN

CLKADPI

SWAKEUP

MMC_CLK

MMC_CMD

MMC_DAT0

MMC_DAT1

MMC_DAT2

MMC_POW

MMC_SDCD

MMC_SDWP

MMC_OBI

CLK32K

MMC_DAT3

DATA4

MMC_DAT4

DATA5

MMC_DAT5

DATA6

MMC_DAT6

DATA7

MMC_DAT7

PER_CLKOUTM2

(192 MHz)

PRCM

/2

CLK_32KHZ

+V

Power Switch

www.ti.com

Integration

Figure 18-3. MMCHS Module MMC Application

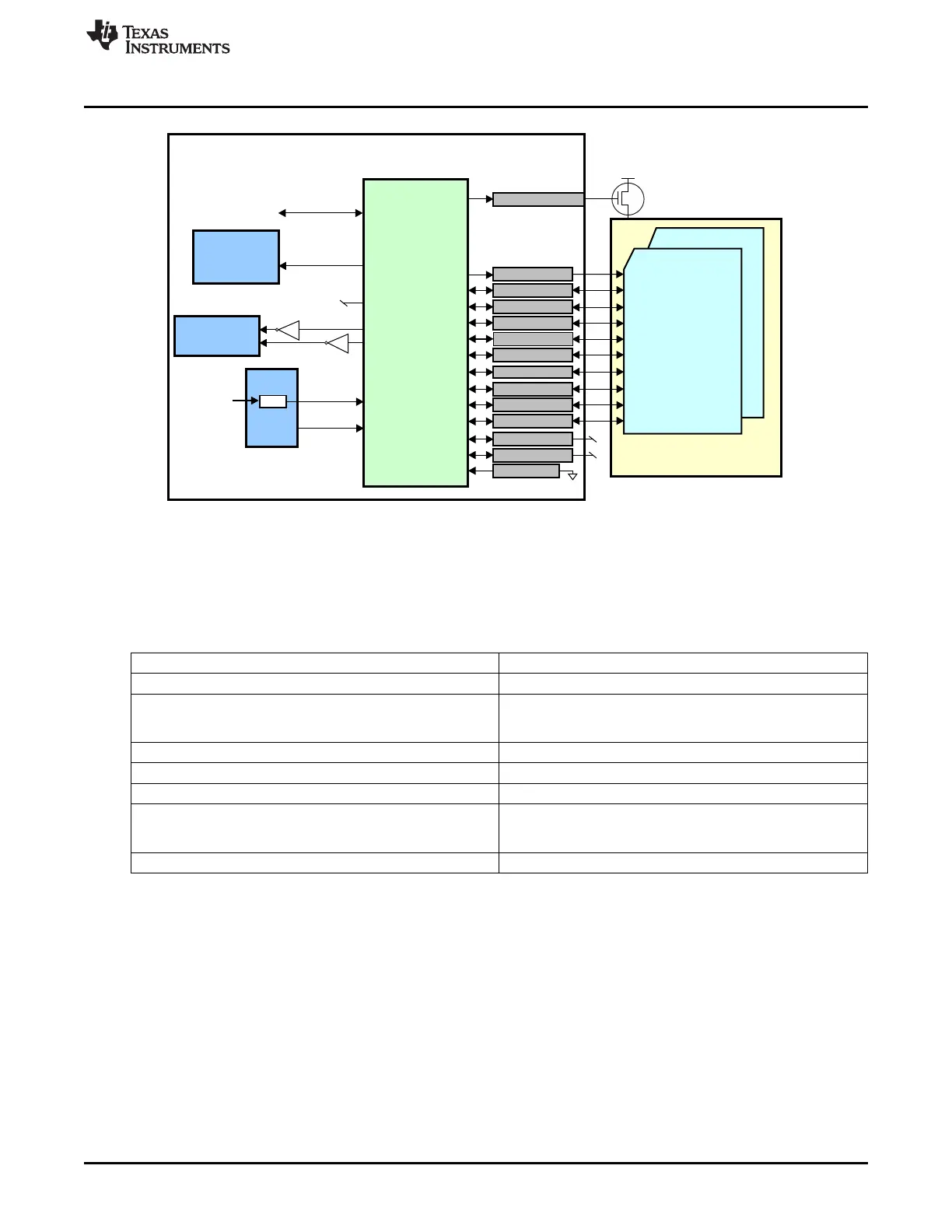

18.2.1 MMCHS Connectivity Attributes

The general connectivity attributes for the three MMCHS modules are shown in Table 18-2.

Table 18-2. MMCHS Connectivity Attributes

Attributes Type

Power Domain Peripheral Domain

Clock Domain PD_PER_L4LS_GCLK (OCP)

PD_PER_MMC_FCLK (Func)

CLK_32KHZ (Debounce)

Reset Signals PER_DOM_RST_N

Idle/Wakeup Signals Smart Idle

Interrupt Requests 1 interrupt per instance to MPU Subsystem (MMCSDxINT)

DMA Requests 2 DMA requests per instance to EDMA (SDTXEVTx,

SDRXEVTx)

(Active low, need to be inverted in glue logic)

Physical Address L4 Peripheral slave port

3347

SPRUH73H–October 2011–Revised April 2013 Multimedia Card (MMC)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...