AHCLKR_IN

AHCLKR_OUT

0

1

1

0

1

0

1

0

1

0

Divider

/1.../4096

HCLKRDIV

(AHCLKRCTL[11-0])

Divider

/1.../32

CLKRDIV

(ACLKRCTL[4-0])

HCLKRP

(Polarity)

(AHCLKRCTL.14)

AUXCLK

HCLKRM

(internal/external)

(AHCLKRCTL.15)

RCLK

ASYNC

(ACLKXCTL.6)

XCLK

(from Figure 16)

CLKRP

(polarity)

(ACLKRCTL.7)

CLKRm

(internal/external)

(ACLKRCTL.5)

Pin Muxing

ACLKR

pin

www.ti.com

Functional Description

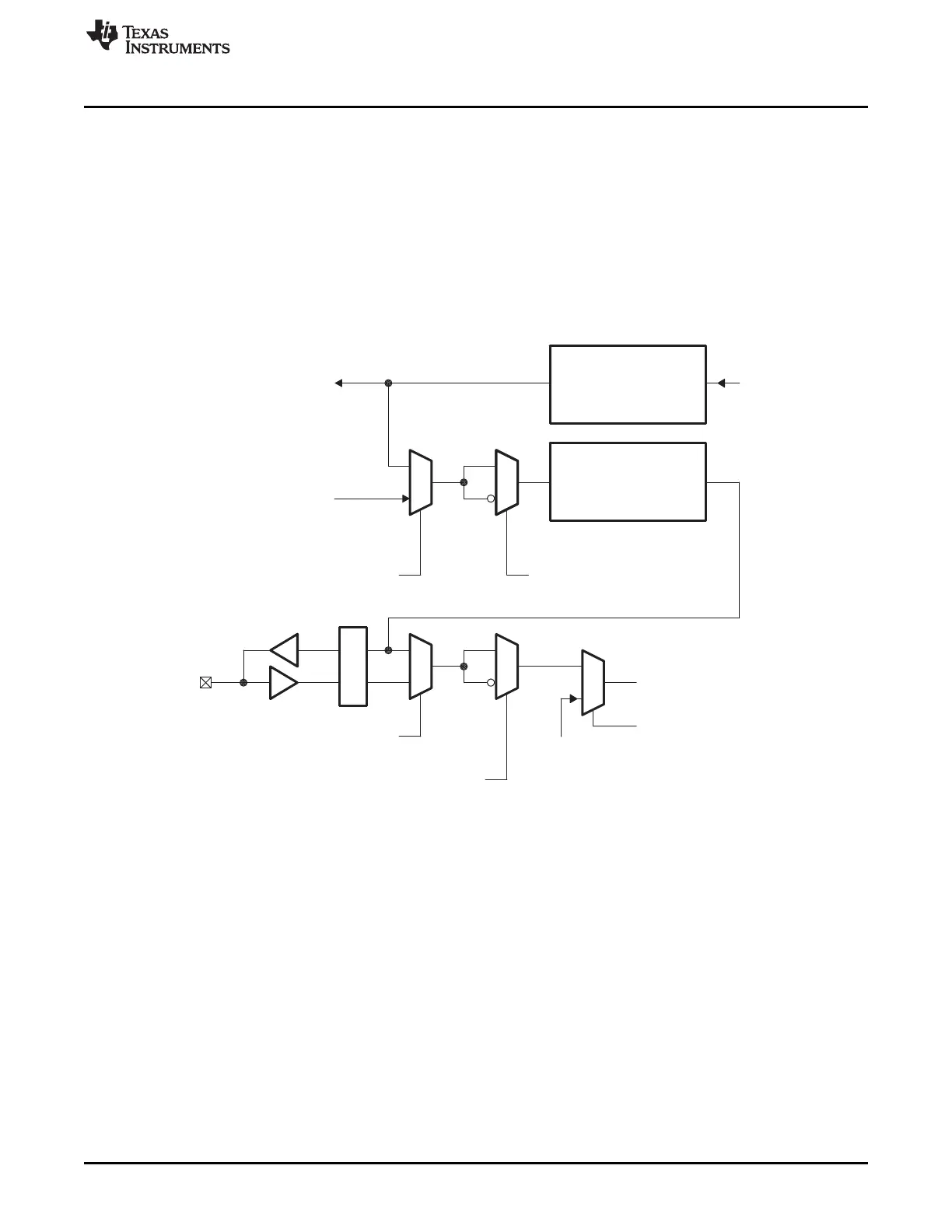

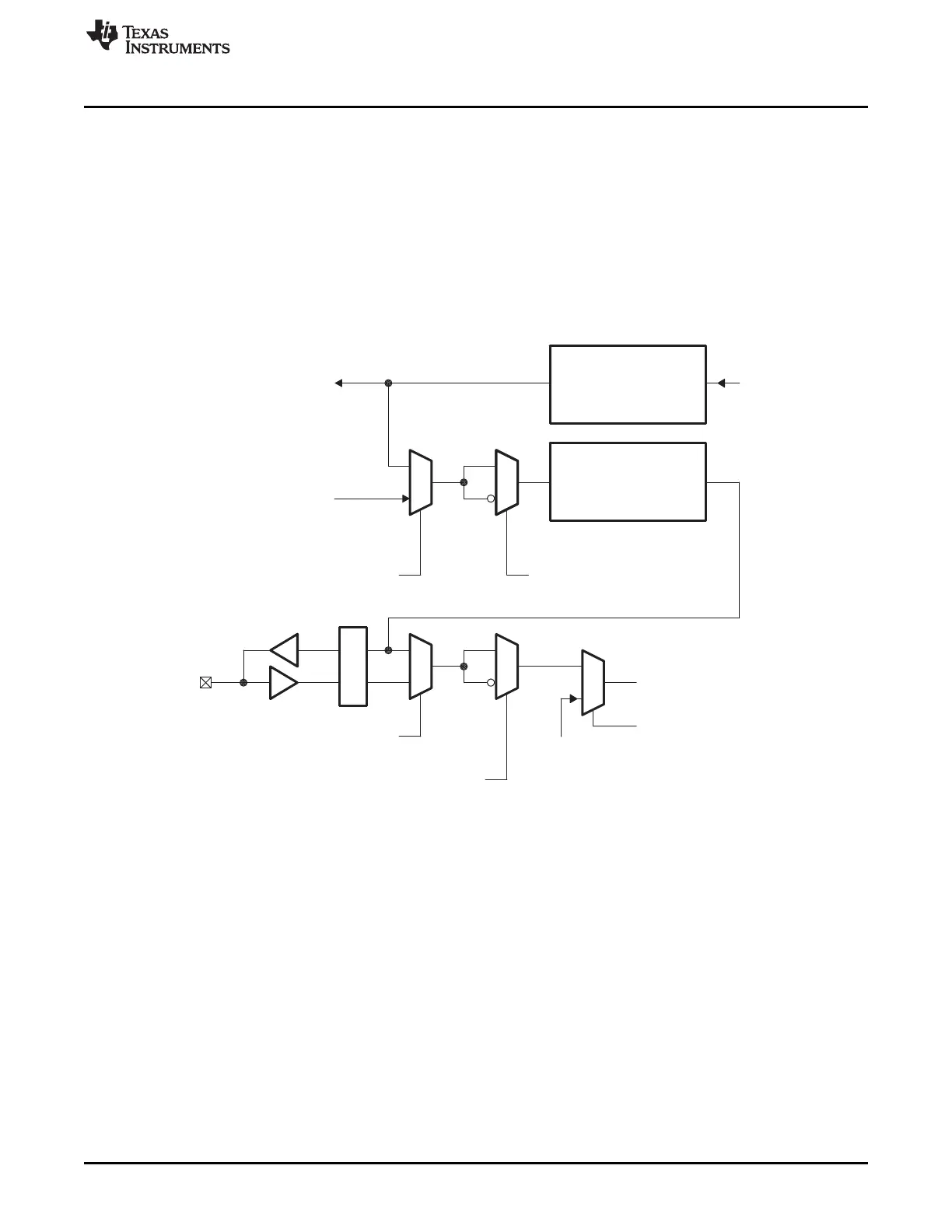

22.3.5.2 Receive Clock

The receiver also has the option to operate synchronously from the ACLKX and AFSX signals. This is

achieved when the ASYNC bit in the transmit clock control register (ACLKXCTL) is cleared to 0 (see

Figure 22-18). The receiver may be configured with different polarity (CLKRP) and frame sync data delay

options from those options of the transmitter.

The receive clock configuration is controlled by the following registers:

• ACLKRCTL.

• AHCLKRCTL.

Figure 22-18. Receive Clock Generator Block Diagram

3785

SPRUH73H–October 2011–Revised April 2013 Multichannel Audio Serial Port (McASP)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...