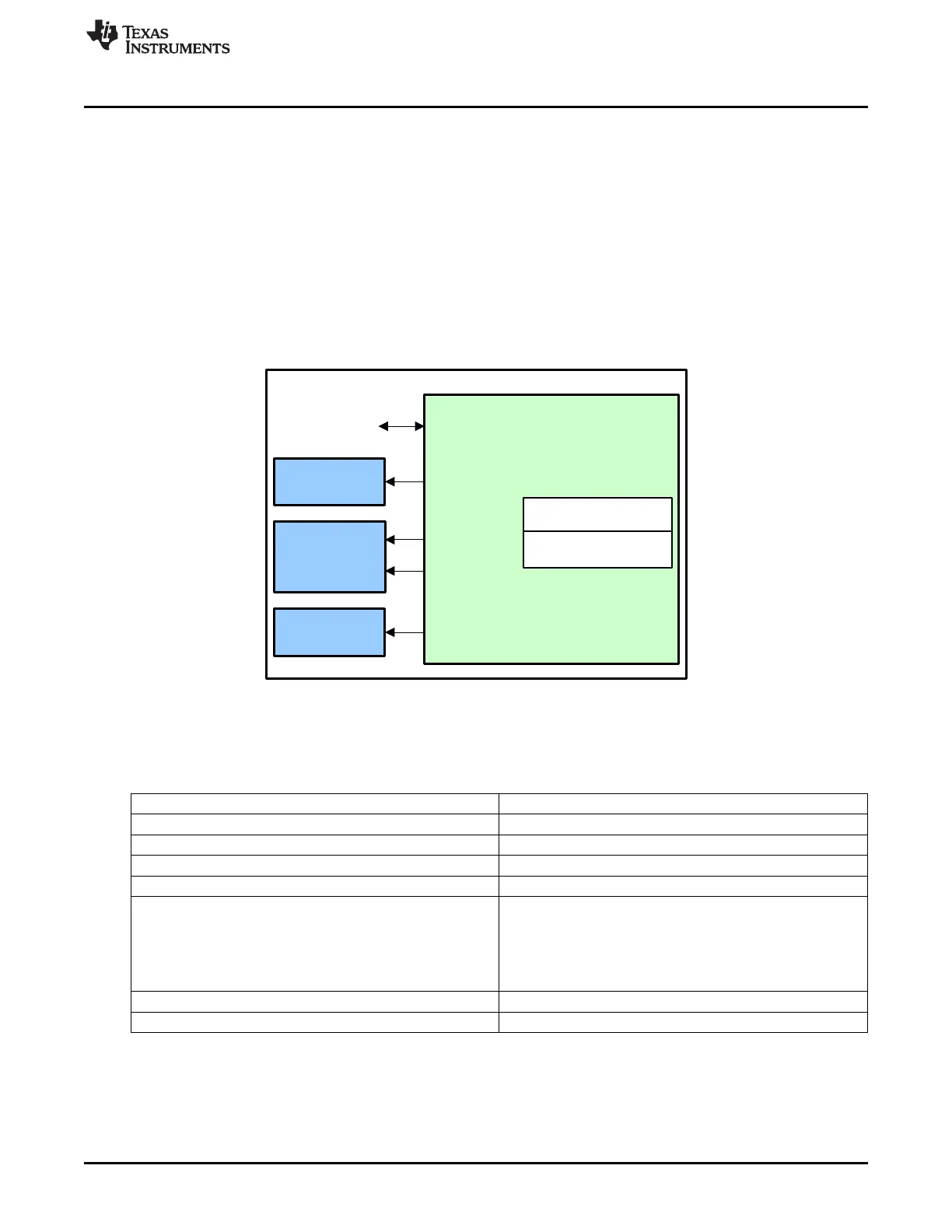

Mailbox

MPU

Subsystem

L4 Peripheral

Interconnect

WakeM3

MAIL_U0_IRQ

MAILBOXn

(4x32-bit messages each)

(x8)

PRU-ICSS

MAIL_U3_IRQ

MAIL_U1_IRQ

MAIL_U2_IRQ

PRU0

PRU1

www.ti.com

Mailbox

17.1.2 Integration

This device contains a single instantiation of the Mailbox module at the system level. The mailbox function

is made of eight sub-module mailboxes each supporting a 1-way communication between two initiators.

The communication protocol from the sender to the receiver is implemented with mailbox registers using

interrupts. The sender sends information to the receiver by writing to the mailbox. Interrupt signaling is

used to notify the receiver a message has been queued or the sender for overflow situation.

The eight mailboxes are enough to handle communications between the MPU Subsystem, PRU-ICSS

PRUs, and WakeM3. Note that because the WakeM3 has access only to L4_Wakeup peripherals it does

not have access to the Mailbox registers. A mailbox interrupt can still be sent to the M3 to trigger message

notification. The actual message payload must be placed in either M3 internal memory or in the Control

Module Interprocessor Message registers (IPC_MSG_REG{0-7}).

Figure 17-1. Mailbox Integration

17.1.2.1 Mailbox Connectivity Attributes

The general connectivity for the Mailbox is shown in Table 17-1.

Table 17-1. Mailbox Connectivity Attributes

Attributes Type

Power Domain Peripheral Domain

Clock Domain L4PER_L4LS_GCLK

Reset Signals PER_DOM_RST_N

Idle/Wakeup Signals Smart Idle

Interrupt Requests

4 Interrupts

mail_u0 (MBINT0) – to MPU Subsystem

mail_u1 – to PRU-ICSS (PRU0)

mail_u2 – to PRU-ICSS (PRU1)

mail_u3 – to WakeM3

DMA Requests None

Physical Address L4 Peripheral slave port

17.1.2.2 Mailbox Clock and Reset Management

The mailbox function operates from the L4 interface clock.

3237

SPRUH73H–October 2011–Revised April 2013 Interprocessor Communication

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...