www.ti.com

GPMC

7.1.5.9 GPMC_CONFIG

The configuration register allows global configuration of the GPMC.

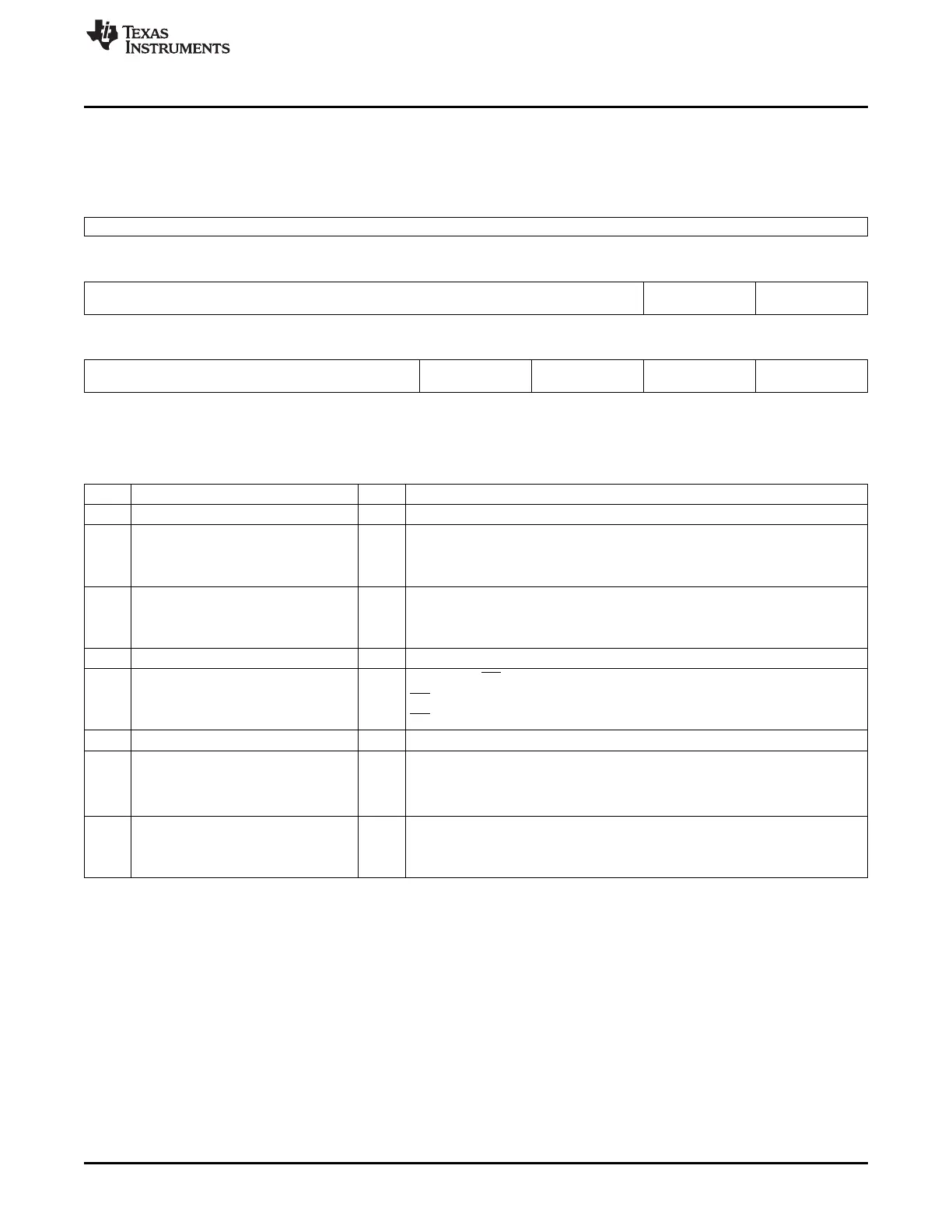

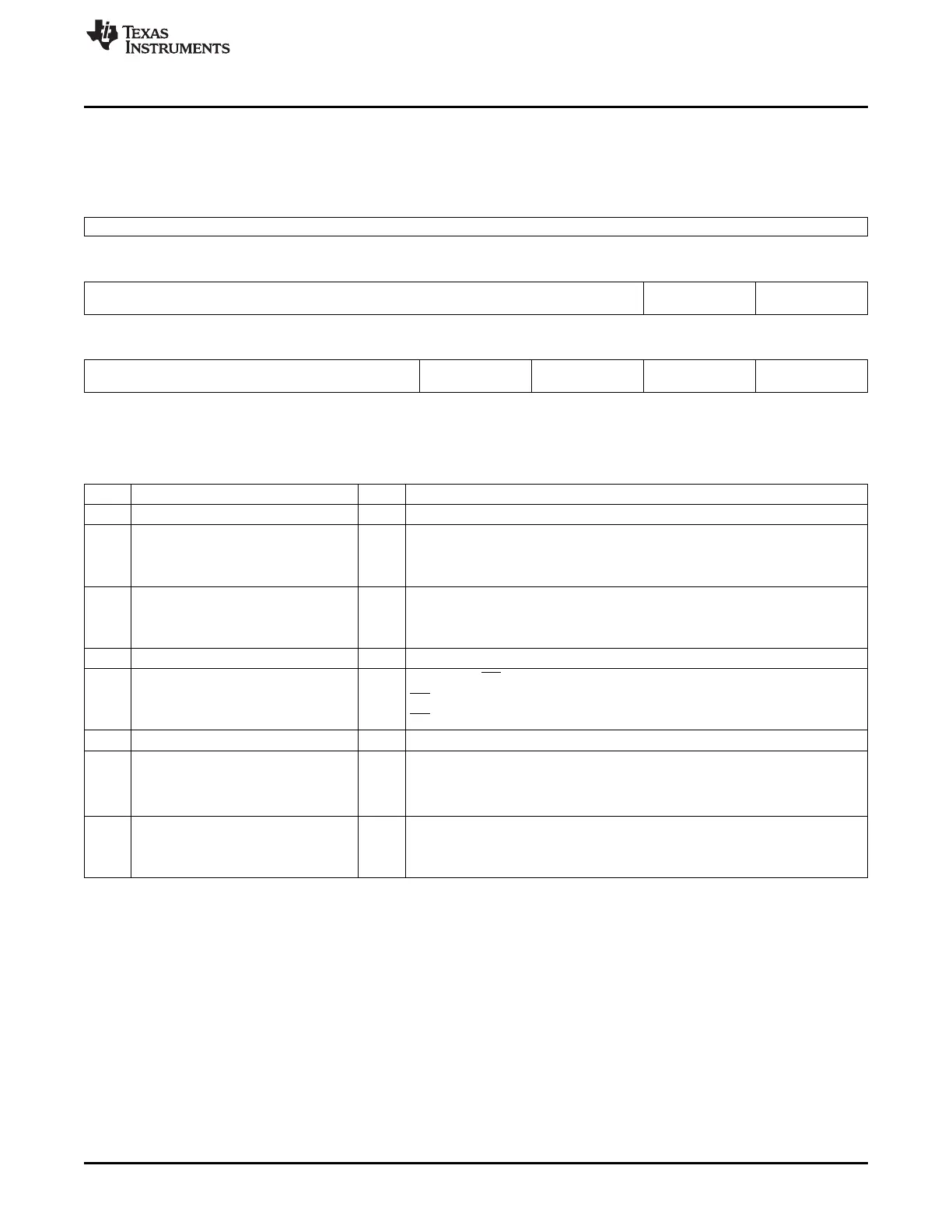

Figure 7-59. GPMC_CONFIG

31 16

Reserved

R-0

15 10 9 8

Reserved WAIT1PIN WAIT0PIN

POLARITY POLARITY

R-0 R/W-0 R/W-0

7 5 4 3 2 1 0

Reserved WRITE Reserved LIMITED NANDFORCE

PROTECT ADDRESS POSTEDWRITE

R-0 R/W-0 R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-63. GPMC_CONFIG Field Descriptions

Bit Field Value Description

31-10 Reserved 0 Reserved

9 WAIT1PINPOLARITY Selects the polarity of input pin WAIT1

0 WAIT1 active low

1 WAIT1 active high

8 WAIT0PINPOLARITY Selects the polarity of input pin WAIT0

0 WAIT0 active low

1 WAIT0 active high

7-5 Reserved 0 Reserved

4 WRITEPROTECT Controls the WP output pin level

0 WP output pin is low

1 WP output pin is high

3-2 Reserved 0 Reserved

1 LIMITEDADDRESS

Limited Address device support

0 No effect. GPMC controls all addresses.

1 A26-A11 are not modified during an external memory access.

0 NANDFORCEPOSTEDWRITE Enables the Force Posted Write feature to NAND Cmd/Add/Data location

0 Disables Force Posted Write

1 Enables Force Posted Write

373

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...