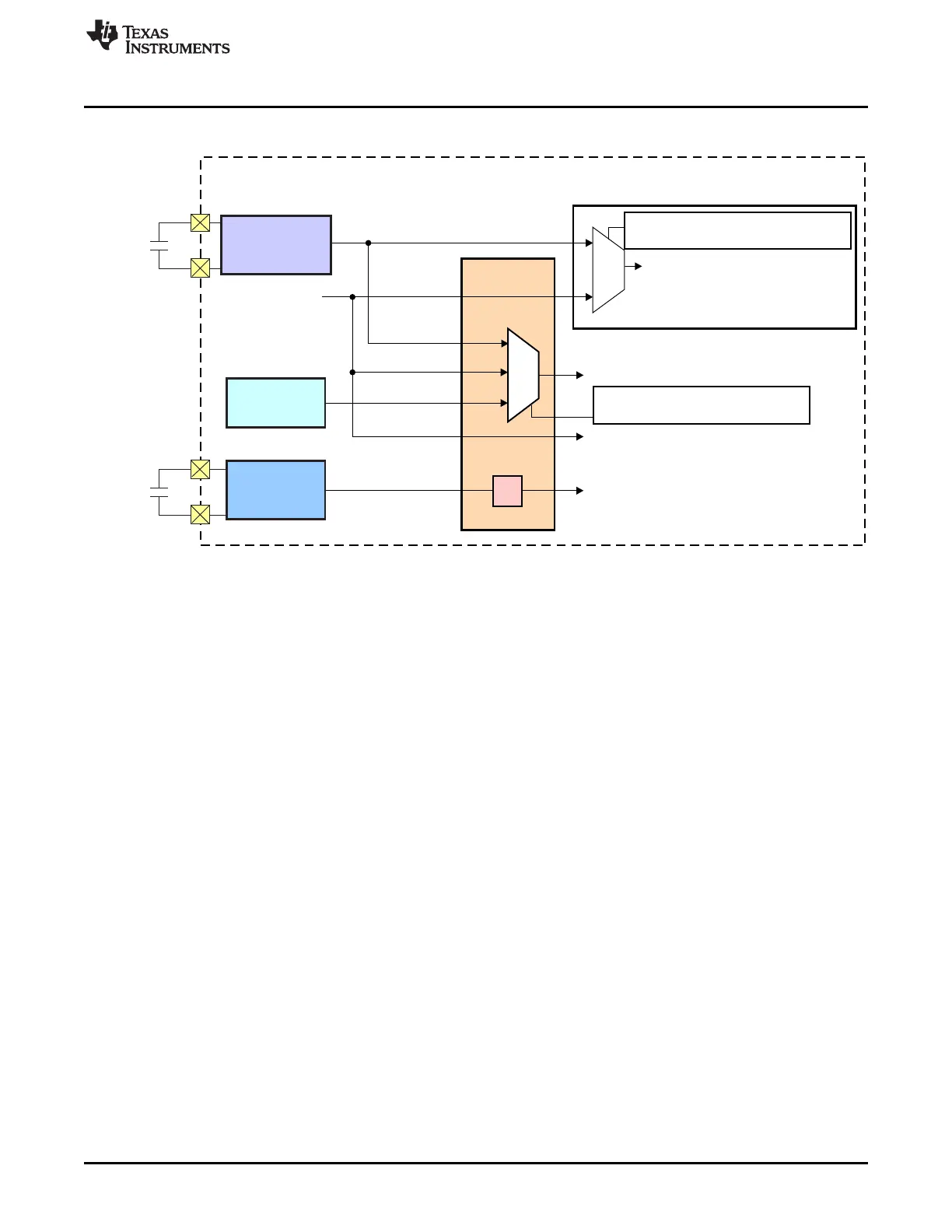

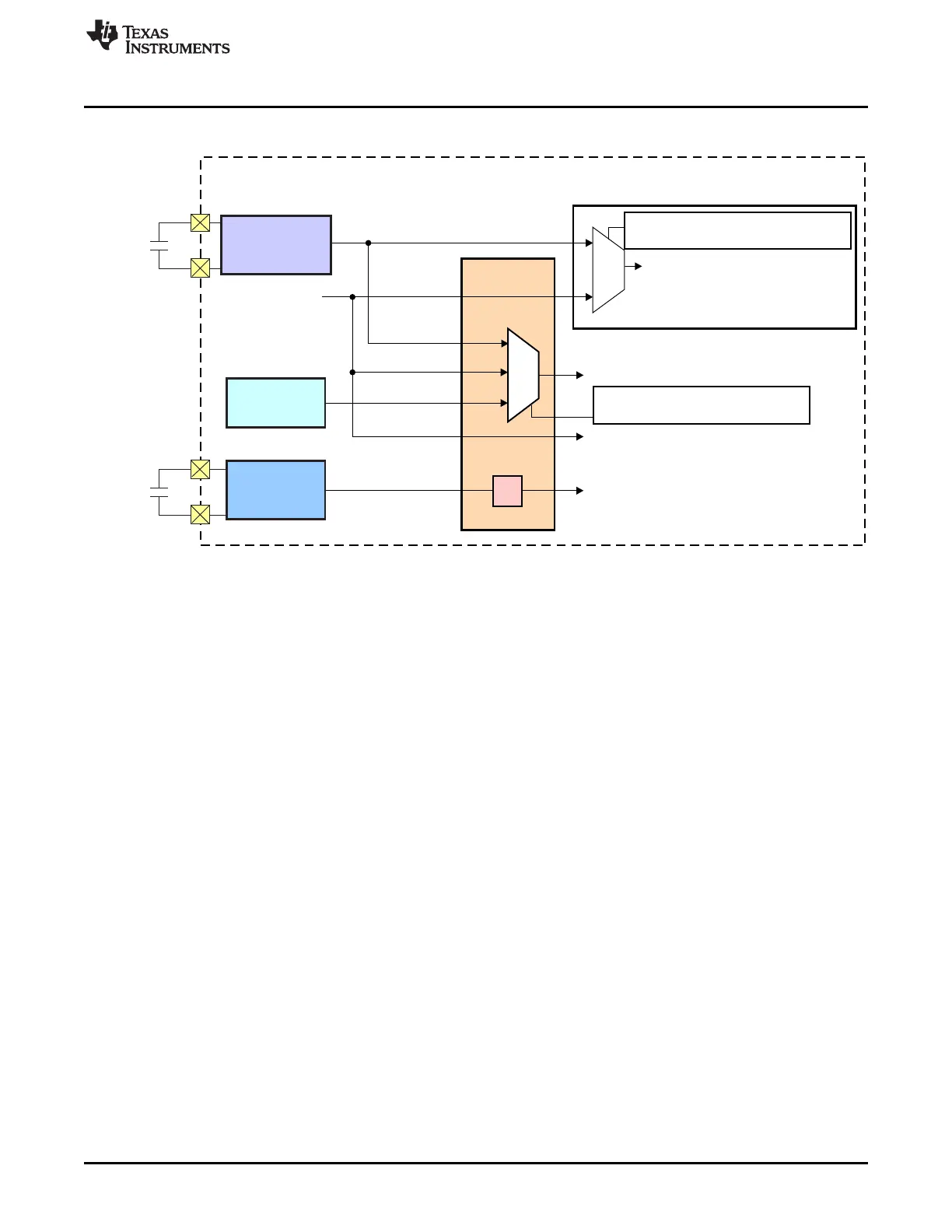

PRCM

2

1

1

0

32,768 Hz

0

To GPIO0 debounce

To VTP

control

RTC IP

RTC clock

PRCM.CLKSEL_GPIO0_DBCLK.

CLKSEL (Reset default = 0)

RTC.OSC_REG.SEL_32KCLK_SRC

(Reset default = 0)

32,768 Hz

Xtal

Device

Xtal

CLK_32KHZ

From PLL

32,768 Hz

Master

Osc

(CLK_M_OSC)

On-Chip

32K RC Osc

(CLK_RC32K)

32K

Osc

(CLK_32K_RTC)

/2

~32,768 Hz

To GPIO{1-6}, MMC, etc.

Debounce

www.ti.com

Power, Reset, and Clock Management

Figure 8-18. RTC, VTP, and Debounce Clock Selection

All mux selections are in PRCM unless explicitly shown otherwise in the diagrams.

8.1.7 Reset Management

8.1.7.1 Overview

The PRCM manages the resets to all power domains inside device and generation of a single reset output

signal through device pin, PWRONRSTn, for external use. The PRCM has no knowledge of or control

over resets generated locally within a module, e.g., via the OCP configuration register bit

IPName_SYSCONFIG.SoftReset.

All PRM reset outputs are asynchronously asserted. These outputs are active-low except for the PLL

resets. Deassertion is synchronous to the clock which runs a counter used to stall, or delay, reset de-

assertion upon source deactivation. This clock will be CLK_M_OSC used by all the reset managers. All

modules receiving a PRCM generated reset are expected to treat the reset as asynchronous and

implement local re-synchronization upon de-activation as needed.

One or more Reset Managers are required per power domain. Independent management of multiple reset

domains is required to meet the reset sequencing requirements of all modules in the power domain

8.1.7.2 Reset Concepts and Definitions

The PRCM collects many sources of reset. Here below is a list of qualifiers of the source of reset:

• Cold reset: it affects all the logic in a given entity

• Warm reset: it is a partial reset which doesn’t affect all the logic in a given entity

• Global reset: it affects the entire device

• Local reset: it affects part of the device (1 power domain for example)

• S/W reset: it is initiated by software

• H/W reset: it is hardware driven

535

SPRUH73H–October 2011–Revised April 2013 Power, Reset, and Clock Management (PRCM)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...