www.ti.com

EMIF

7.3.5.11 SDRAM_TIM_3 Register (offset = 28h) [reset = 0h]

SDRAM_TIM_3 is shown in Figure 7-101 and described in Table 7-121.

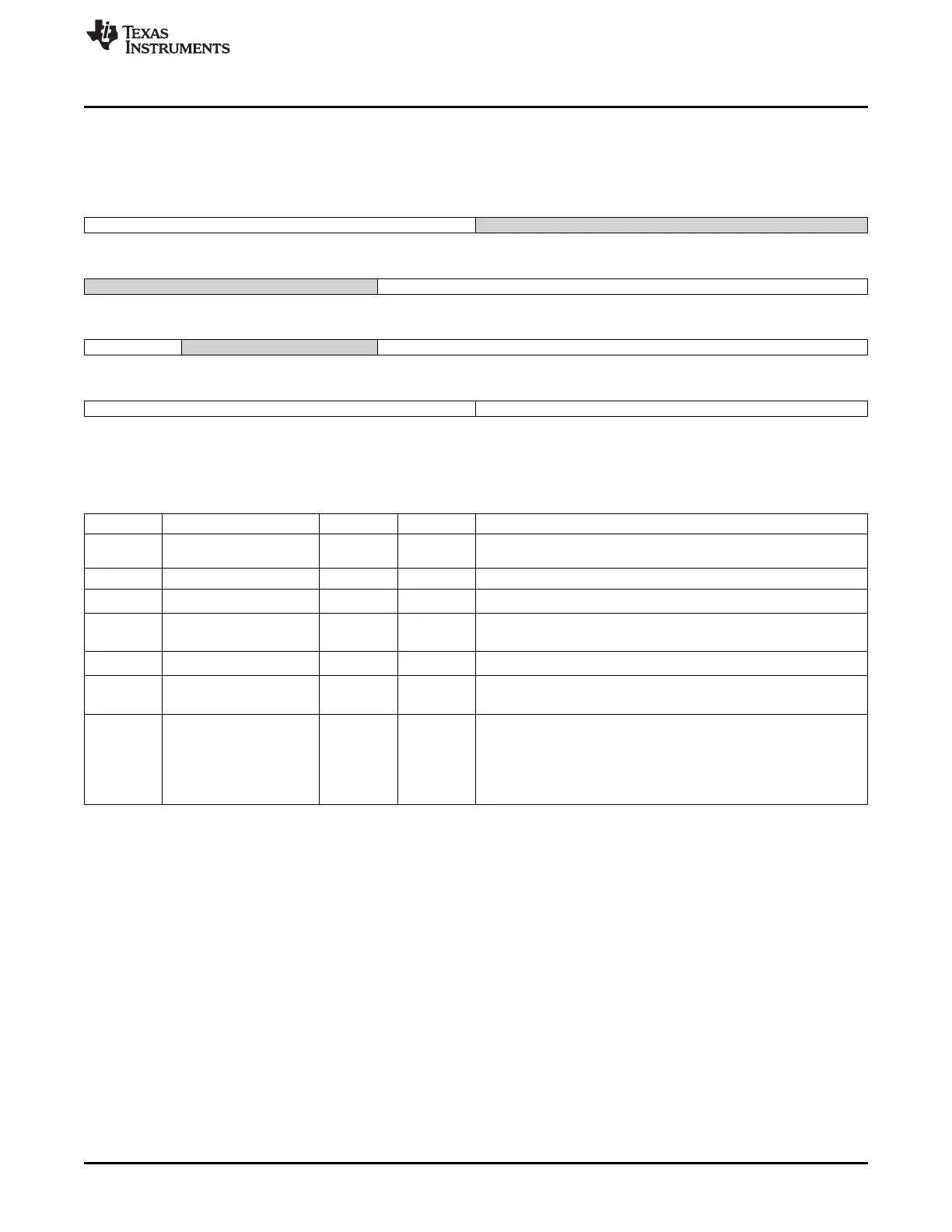

Figure 7-101. SDRAM_TIM_3 Register

31 30 29 28 27 26 25 24

reg_t_pdll_ul Reserved

R/W-0h R-0h

23 22 21 20 19 18 17 16

Reserved reg_zq_zqcs

R/W-0h R/W-0h

15 14 13 12 11 10 9 8

reg_zq_zqcs Reserved reg_t_rfc

R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

reg_t_rfc reg_t_ras_max

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

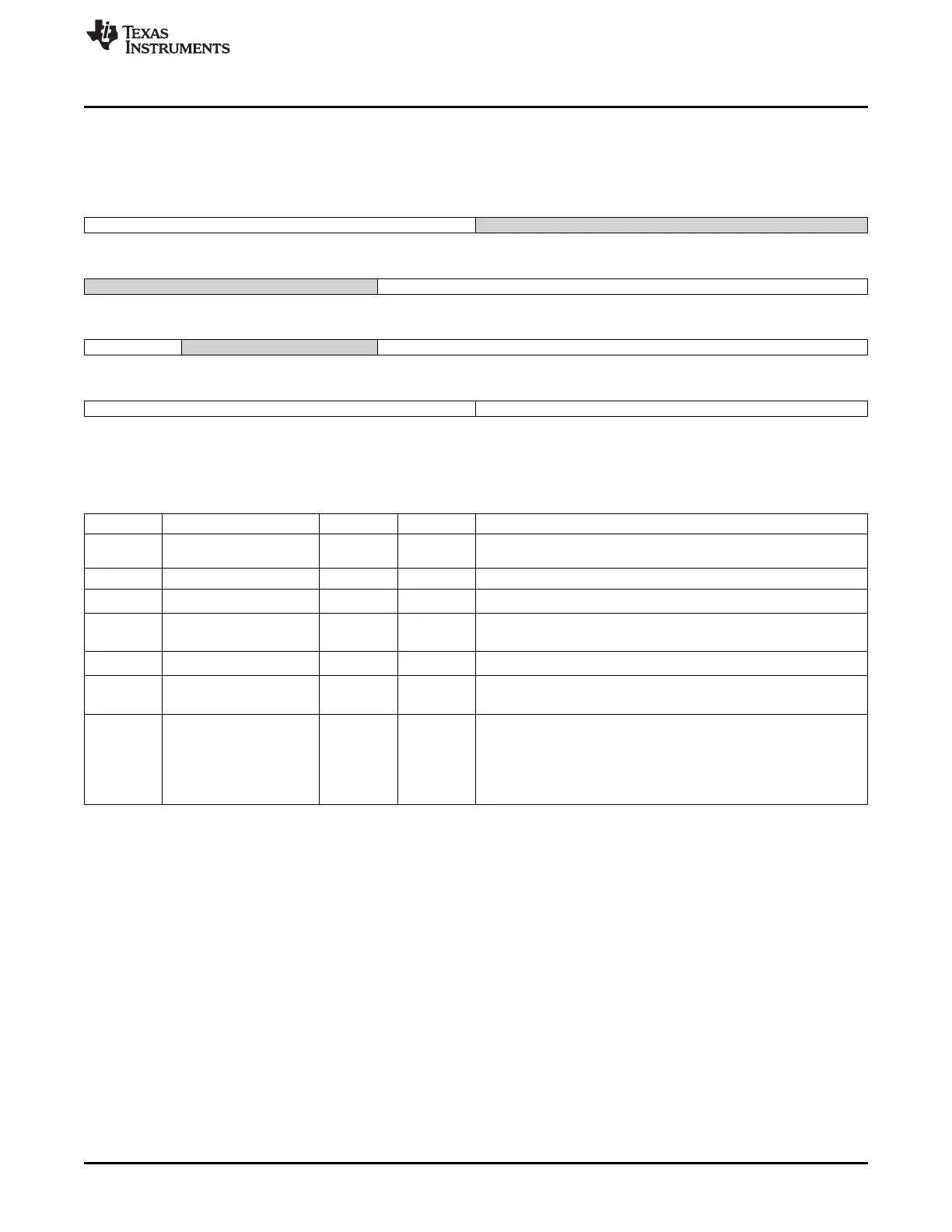

Table 7-121. SDRAM_TIM_3 Register Field Descriptions

Bit Field Type Reset Description

31-28 reg_t_pdll_ul R/W 0h Minimum number of DDR clock cycles for PHY DLL to unlock.

A value of N will be equal to N x 128 clocks.

27-24 Reserved R 0h

23-21 Reserved R/W 0h

Reserved.

20-15 reg_zq_zqcs R/W 0h

Number of DDR clock clock cycles for a ZQCS command, minus

one.

14-13 Reserved R/W 0h

Reserved.

12-4 reg_t_rfc R/W 0h

Minimum number of DDR clock cycles from Refresh or Load Mode to

Refresh or Activate, minus one.

3-0 reg_t_ras_max R/W 0h Maximum number of reg_refresh_rate intervals from Activate to

Precharge command.

This field must be equal to ((tRASmax / tREFI)-1) rounded down to

the next lower integer.

This field is only applicable for mDDR.

This field must be programmed to 0xF for other SDRAM types.

435

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...