EMIF

www.ti.com

7.3.2 Integration

7.3.2.1 EMIF Connectivity Attributes

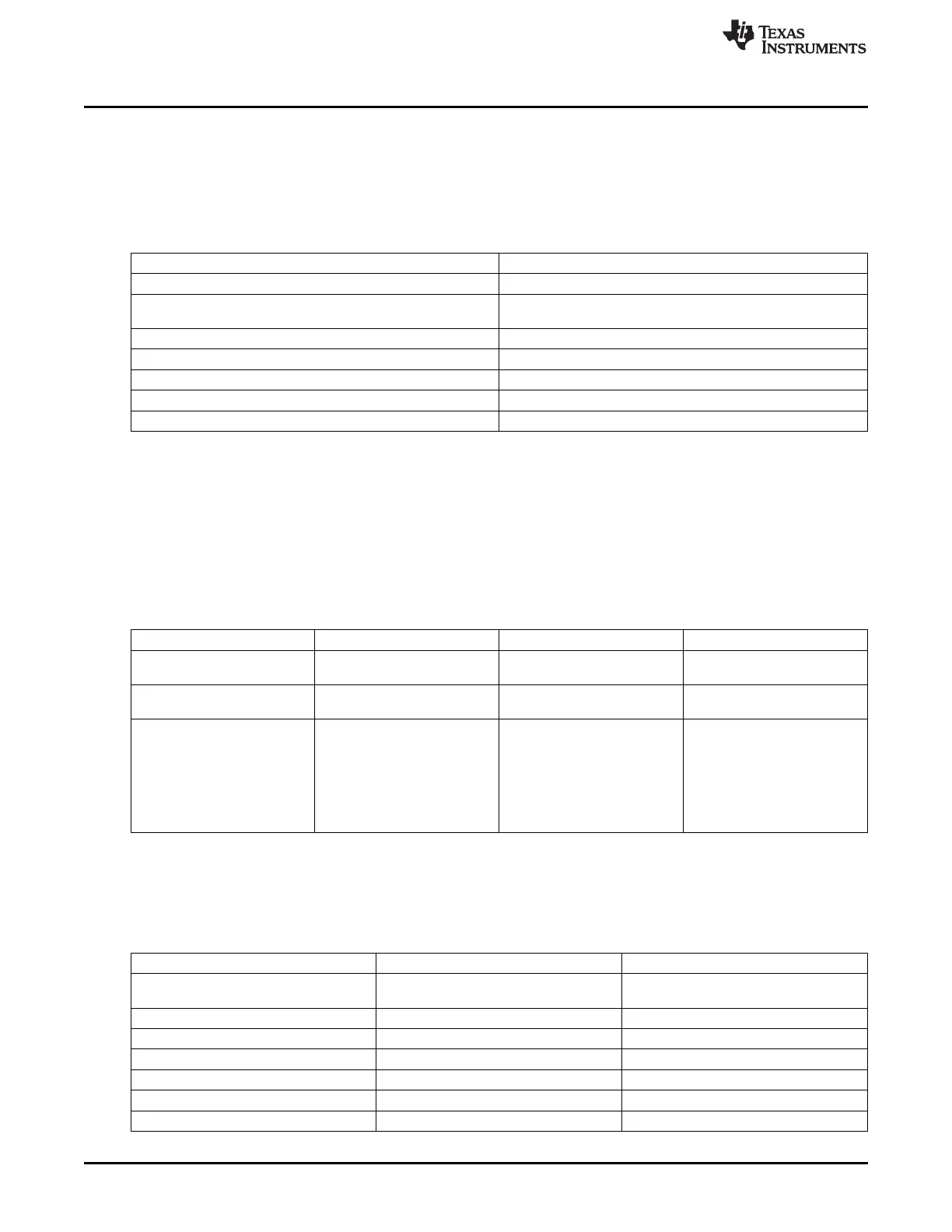

The general connectivity attributes for the EMIF are shown in Table 7-94.

Table 7-94. EMIF Connectivity Attributes

Attributes Type

Power Domain Peripheral Domain

Clock Domain PD_PER_L3_GCLK (OCP)

PD_PER_EMIF_GCLK (Func)

Reset Signals POR_N

Idle/Wakeup Signals Smart Idle

Interrupt Requests 1 interrupt to MPU Subsystem (DDRERR0)

DMA Requests None

Physical Address L3 Fast Slave Port

7.3.2.2 EMIF Clock Management

The EMIF4 OCP interface (ocp_clk) is clocked by the L3 Fast clock sourced from the Core PLL. The DDR

Command and Data macros are clocked by the DDR PLL. The PRCM divides this clock by two to create

the EMIF functional clock (m_clk).

The OCP and functional clocks may be asynchronous because synchronization is managed in the EMIF4

internal FIFO (EMIF4 is set in asynchronous mode).

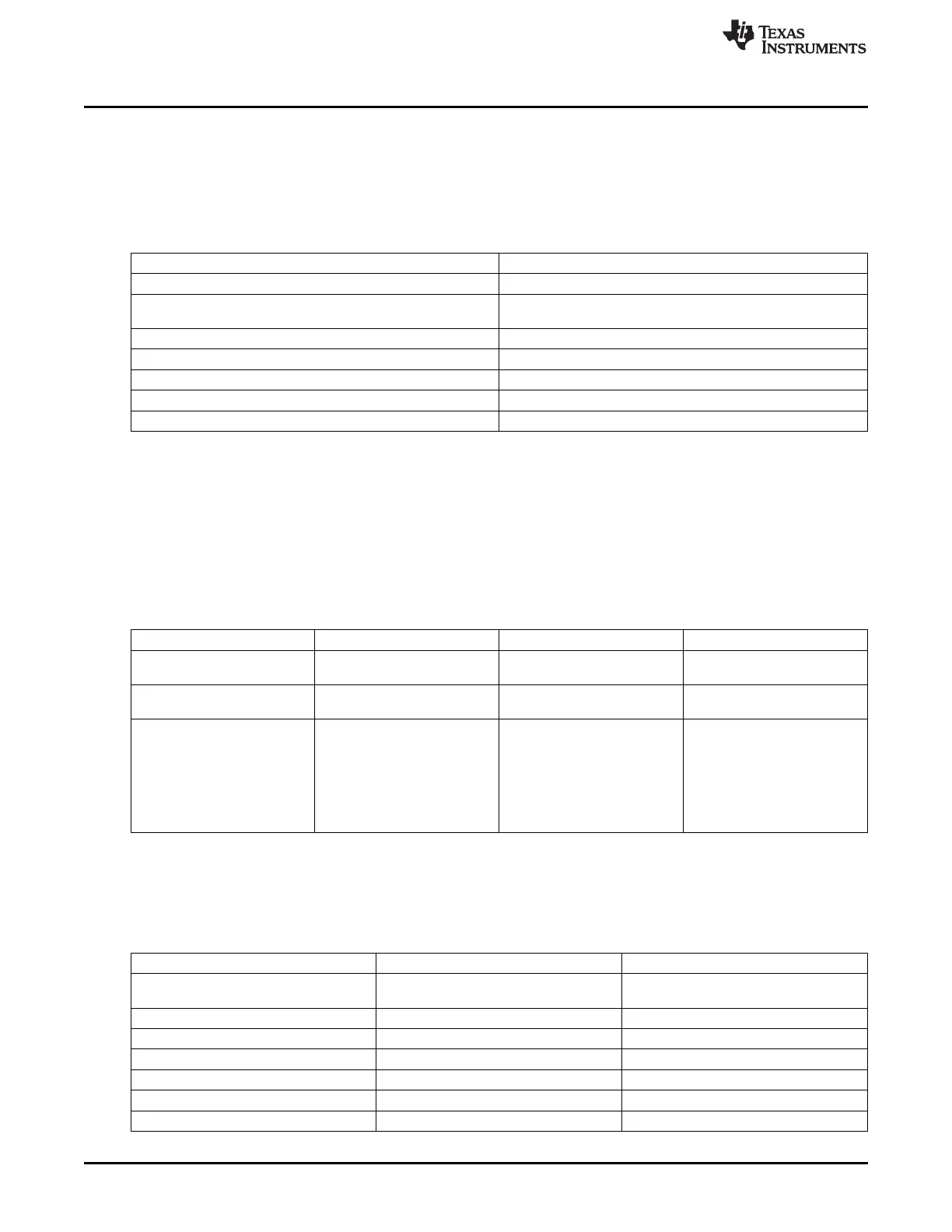

Table 7-95. EMIF Clock Signals

Clock Signal Maximum Frequency Reference Source Comments

ocp_clk 200 MHz CORE_CLKOUTM4 pd_per_l3_gclk

(Interface clock) From PRCM

m_clk 152 MHz DDR PLL CLKOUT / 2 pd_per_emif_gclk

(EMIF functional clock) From PRCM

400 MHz DDR PLL CLKOUT clkout_po

cmd0_dfi_clk

From DDR PLL

cmd1_dfi_clk

cmd2_dfi_clk

data0_dfi_clk

data1_dfi_clk

(Macro clocks)

7.3.2.3 EMIF Pin List

The EMIF/DDR external interface signals are shown in Table 7-96.

Table 7-96. EMIF Pin List

Pin Type Description

DDR_CK O Differential clock pair

DDR_NCK

DDR_CKE O Clock enable

DDR_CSn0 O Chip select

DDR_RASn O Row address strobe

DDR_CASn O Column address strobe

DDR_WEn O Write enable

DDR_BA[2:0] O Bank address

402

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...