www.ti.com

EDMA3 Registers

11.4 EDMA3 Registers

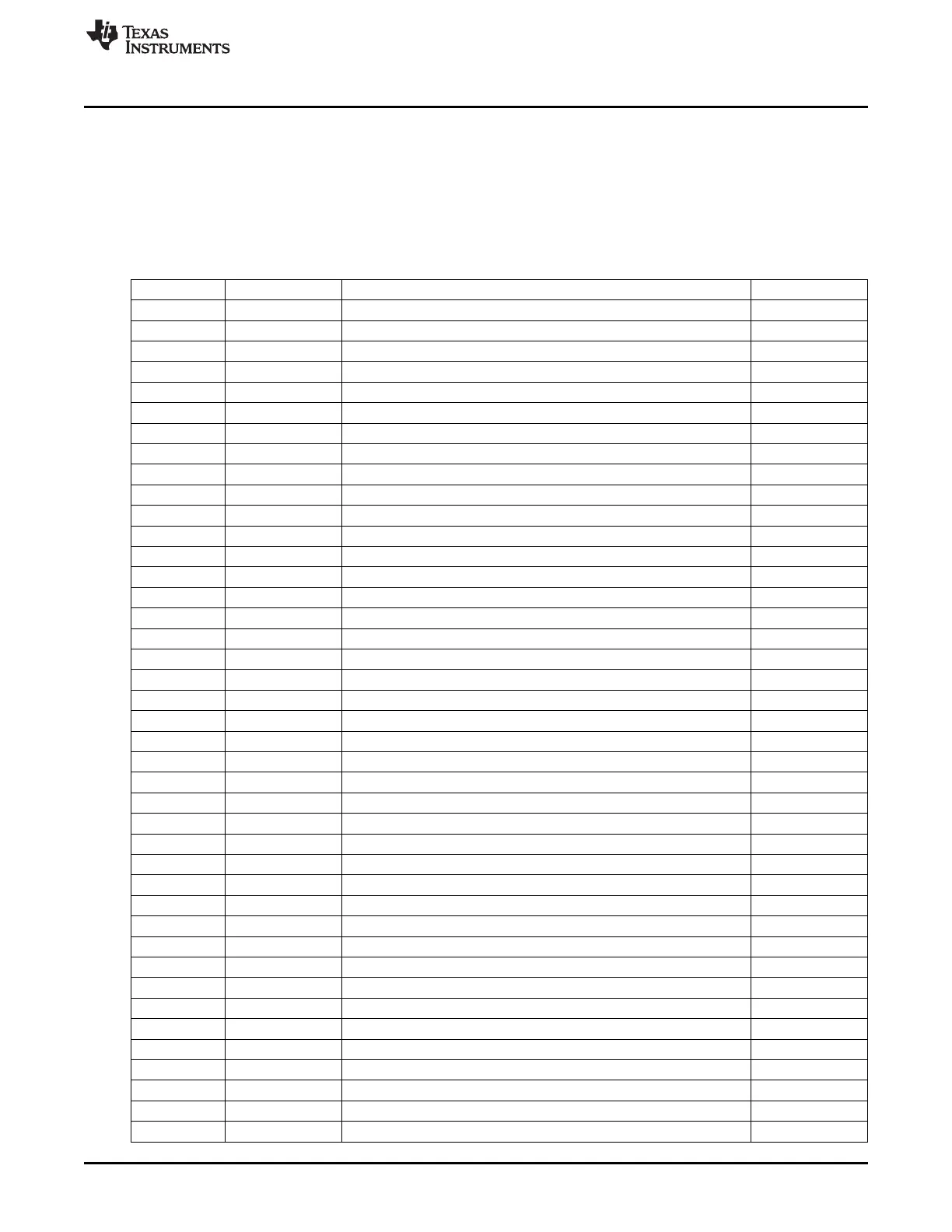

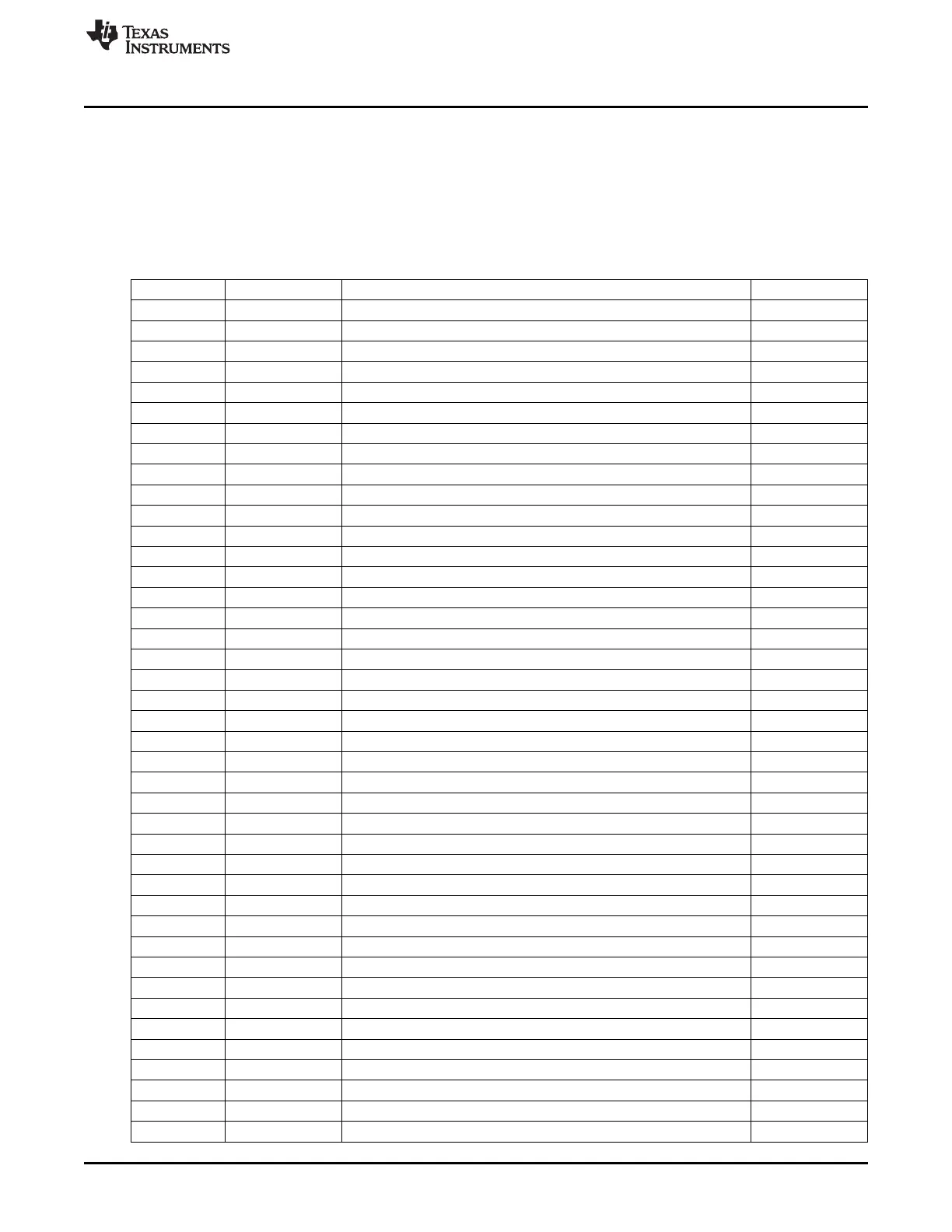

11.4.1 EDMA3 Channel Controller Registers

Table 11-25 lists the memory-mapped registers for the EDMA3 channel controller (EDMACC). All other

register offset addresses not listed in Table 11-25 should be considered as reserved locations and the

register contents should not be modified.

Table 11-25. EDMACC Registers

Offset Acronym Register Description Section

00h PID Peripheral Identification Register Section 11.4.1.1.1

04h CCCFG EDMA3CC Configuration Register Section 11.4.1.1.2

10h SYSCONFIG EDMA3CC System Configuration Register Section 11.4.1.1.3

0100h-01FCh DCHMAP0-63 DMA Channel 0-63 Mapping Registers Section 11.4.1.1.4

0200h QCHMAP0 QDMA Channel 0 Mapping Register Section 11.4.1.1.5

0204h QCHMAP1 QDMA Channel 1 Mapping Register Section 11.4.1.1.5

0208h QCHMAP2 QDMA Channel 2 Mapping Register Section 11.4.1.1.5

020Ch QCHMAP3 QDMA Channel 3 Mapping Register Section 11.4.1.1.5

0210h QCHMAP4 QDMA Channel 4 Mapping Register Section 11.4.1.1.5

0214h QCHMAP5 QDMA Channel 5 Mapping Register Section 11.4.1.1.5

0218h QCHMAP6 QDMA Channel 6 Mapping Register Section 11.4.1.1.5

021Ch QCHMAP7 QDMA Channel 7 Mapping Register Section 11.4.1.1.5

0240h DMAQNUM0 DMA Queue Number Register 0 Section 11.4.1.1.6

0244h DMAQNUM1 DMA Queue Number Register 1 Section 11.4.1.1.6

0248h DMAQNUM2 DMA Queue Number Register 2 Section 11.4.1.1.6

024Ch DMAQNUM3 DMA Queue Number Register 3 Section 11.4.1.1.6

0250h DMAQNUM4 DMA Queue Number Register 4 Section 11.4.1.1.6

0254h DMAQNUM5 DMA Queue Number Register 5 Section 11.4.1.1.6

0258h DMAQNUM6 DMA Queue Number Register 6 Section 11.4.1.1.6

025Ch DMAQNUM7 DMA Queue Number Register 7 Section 11.4.1.1.6

0260h QDMAQNUM QDMA Queue Number Register Section 11.4.1.1.7

0284h QUEPRI Queue Priority Register Section 11.4.1.1.8

0300h EMR Event Missed Register Section 11.4.1.2.1

0304h EMRH Event Missed Register High Section 11.4.1.2.1

0308h EMCR Event Missed Clear Register Section 11.4.1.2.2

030Ch EMCRH Event Missed Clear Register High Section 11.4.1.2.2

0310h QEMR QDMA Event Missed Register Section 11.4.1.2.3

0314h QEMCR QDMA Event Missed Clear Register Section 11.4.1.2.4

0318h CCERR EDMA3CC Error Register Section 11.4.1.2.5

031Ch CCERRCLR EDMA3CC Error Clear Register Section 11.4.1.2.6

0320h EEVAL Error Evaluate Register Section 11.4.1.2.7

0340h DRAE0 DMA Region Access Enable Register for Region 0 Section 11.4.1.3.1

0344h DRAEH0 DMA Region Access Enable Register High for Region 0 Section 11.4.1.3.1

0348h DRAE1 DMA Region Access Enable Register for Region 1 Section 11.4.1.3.1

034Ch DRAEH1 DMA Region Access Enable Register High for Region 1 Section 11.4.1.3.1

0350h DRAE2 DMA Region Access Enable Register for Region 2 Section 11.4.1.3.1

0354h DRAEH2 DMA Region Access Enable Register High for Region 2 Section 11.4.1.3.1

0358h DRAE3 DMA Region Access Enable Register for Region 3 Section 11.4.1.3.1

035Ch DRAEH3 DMA Region Access Enable Register High for Region 3 Section 11.4.1.3.1

0360h DRAE4 DMA Region Access Enable Register for Region 4 Section 11.4.1.3.1

0364h DRAEH4 DMA Region Access Enable Register High for Region 4 Section 11.4.1.3.1

939

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...