www.ti.com

I2C Registers

21.4.1.8 I2C_WE Register (offset = 34h) [reset = 0h]

I2C_WE is shown in Figure 21-23 and described in Table 21-16.

Every 1-bit field in the I2C_WE register enables a specific (synchronous) IRQ request source to generate

an asynchronous wakeup (on the appropriate swakeup line). When a bit location is set to 1 by the local

host, a wakeup is signaled to the local host if the corresponding event is captured by the core of the I2C

controller. Value after reset is low (all bits). There is no need for an Access Error WakeUp event, since

this event occurs only when the module is in Active Mode (for Interface/OCP accesses to FIFO) and is

signaled by an interrupt. With the exception of Start Condition WakeUp, which is asynchronously detected

when the Functional clock is turned-off, all the other WakeUp events require the Functional (System) clock

to be enabled.

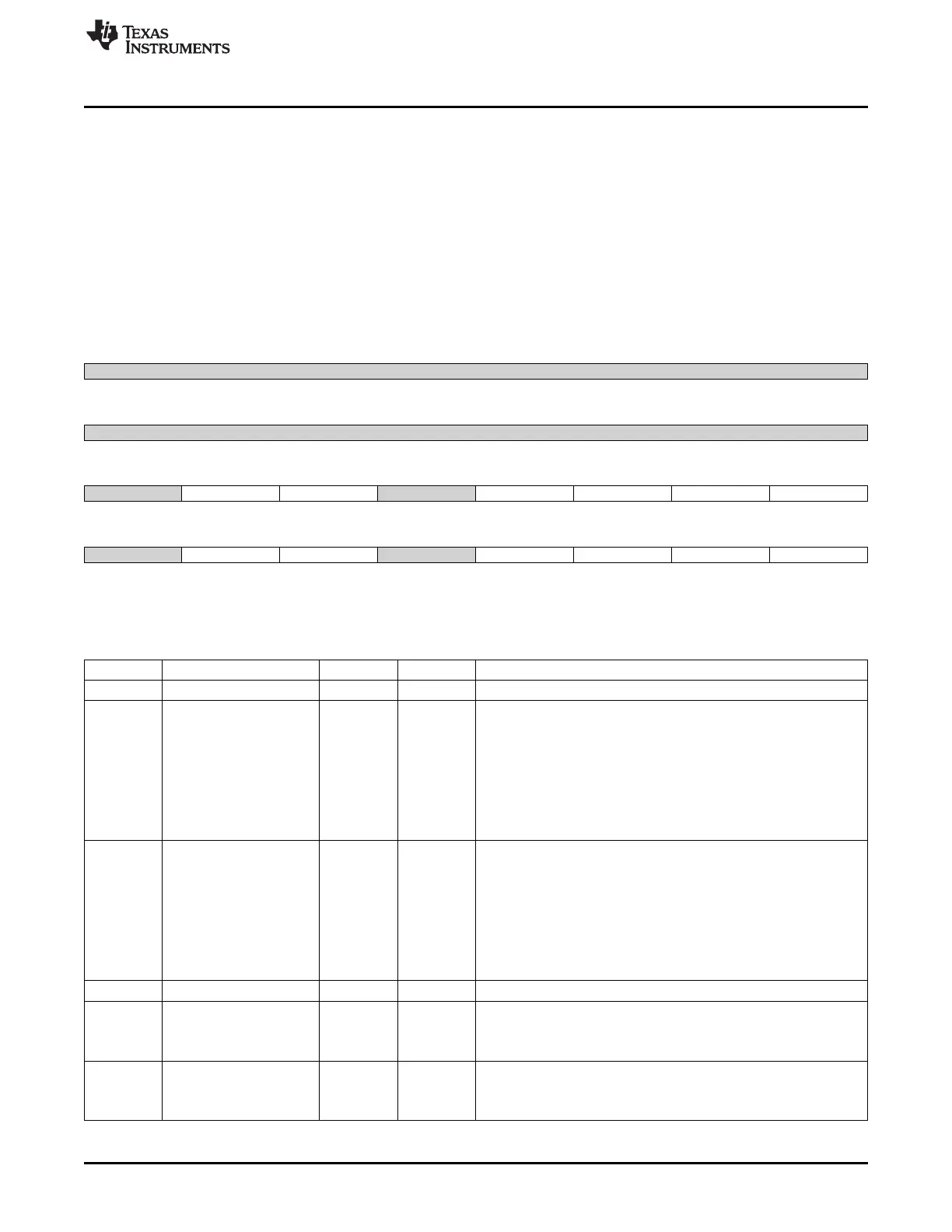

Figure 21-23. I2C_WE Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved XDR_WE RDR_WE Reserved ROVR_WE XUDF_WE AAS_WE BF_WE

R-0h R/W-0h R/W-0h R-0h R/W-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

Reserved STC_WE GC_WE Reserved DRDY_WE ARDY_WE NACK_WE AL_WE

R-0h R/W-0h R/W-0h R-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

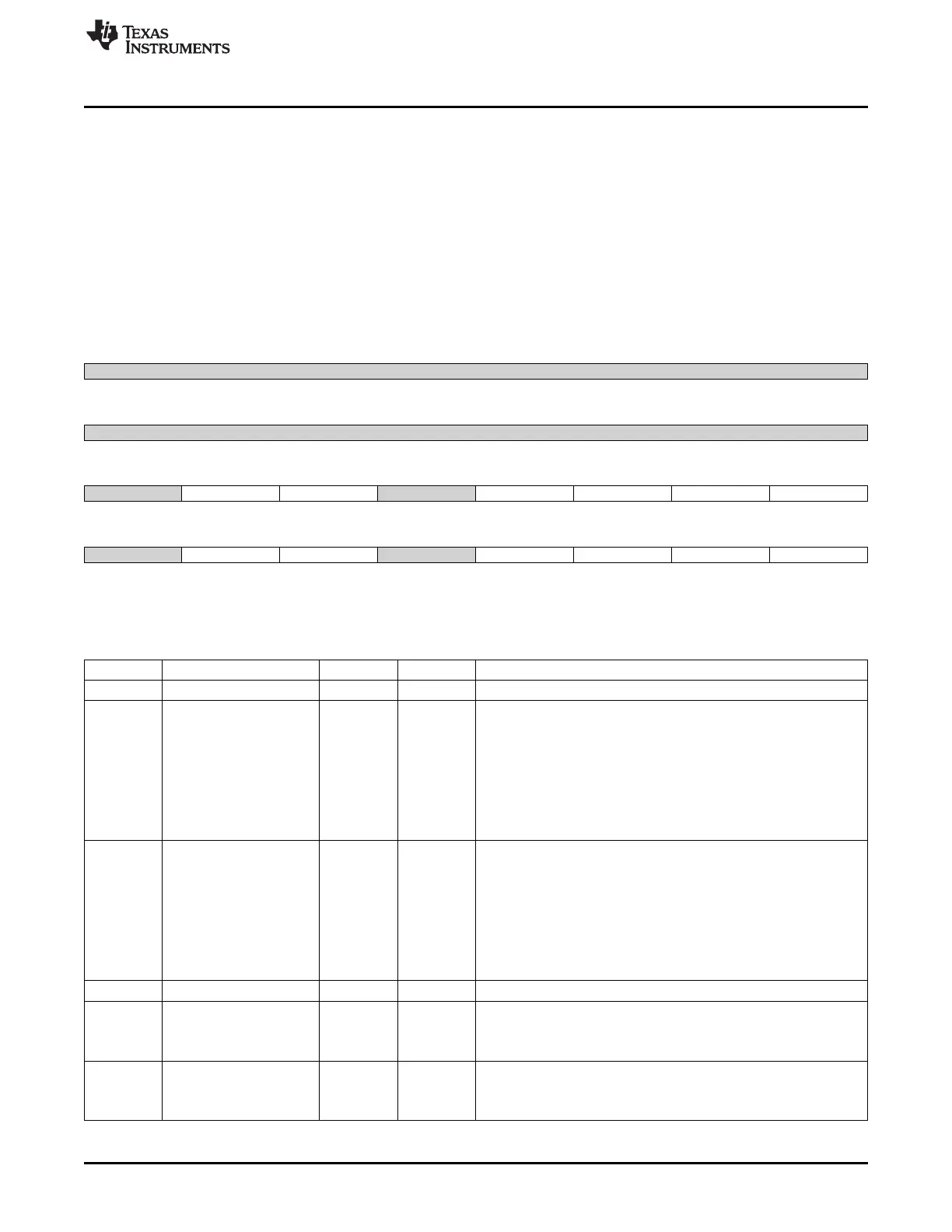

Table 21-16. I2C_WE Register Field Descriptions

Bit Field Type Reset Description

31-15 Reserved R 0h

14 XDR_WE R/W 0h Transmit draining wakeup enable.

This read/write bit is used to enable or disable wakeup signal

generation when I2C module is in idle mode, the TX FIFO level is

below the threshold and the amount of data left to be transferred is

less than TXTRSH value.

This allows for the module to inform the CPU that it can check the

amount of data to be written to the FIFO.

0x0 = Transmit draining wakeup disabled

0x1 = Transmit draining wakeup enabled

13 RDR_WE R/W 0h Receive draining wakeup enable.

This read/write bit is used to enable or disable wakeup signal

generation when I2C is in idle mode, configured as a receiver, and it

has detected a stop condition on the bus but the RX FIFO threshold

is not reached (but the FIFO is not empty).

This allows for the module to inform the CPU that it can check the

amount of data to be transferred from the FIFO.

0x0 = Receive draining wakeup disabled

0x1 = Receive draining wakeup enabled

12 Reserved R 0h

11 ROVR_WE R/W 0h

Receive overrun wakeup enable

0x0 = Receive overrun wakeup disabled

0x1 = Receive overrun wakeup enabled

10 XUDF_WE R/W 0h

Transmit underflow wakeup enable

0x0 = Transmit underflow wakeup disabled

0x1 = Transmit underflow wakeup enabled

3733

SPRUH73H–October 2011–Revised April 2013 I2C

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...