Ethernet Subsystem Registers

www.ti.com

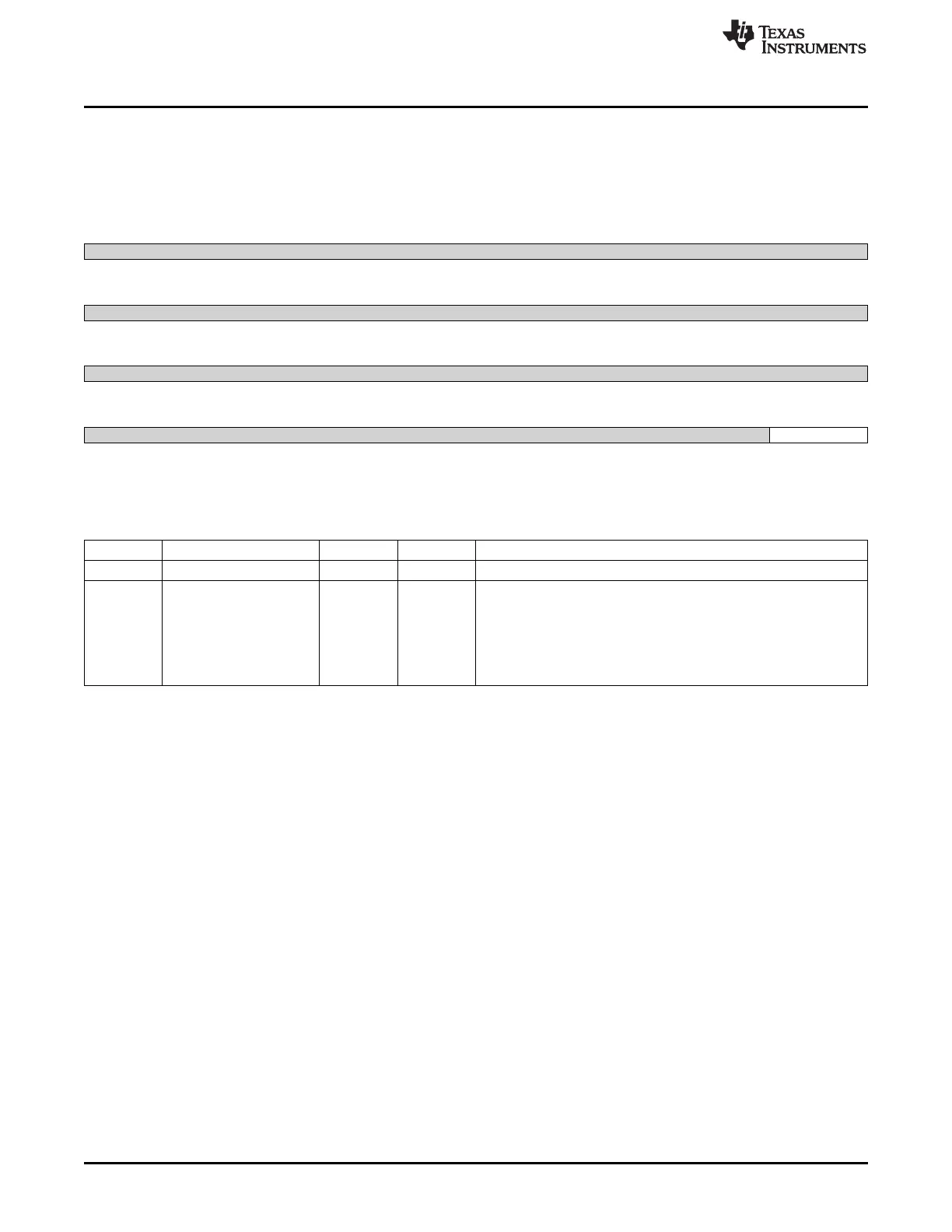

14.5.3.9 CPTS_EVENT_POP Register (offset = 30h) [reset = 0h]

CPTS_EVENT_POP is shown in Figure 14-86 and described in Table 14-98.

EVENT INTERRUPT POP REGISTER

Figure 14-86. CPTS_EVENT_POP Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved EVENT_POP

R-0h W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

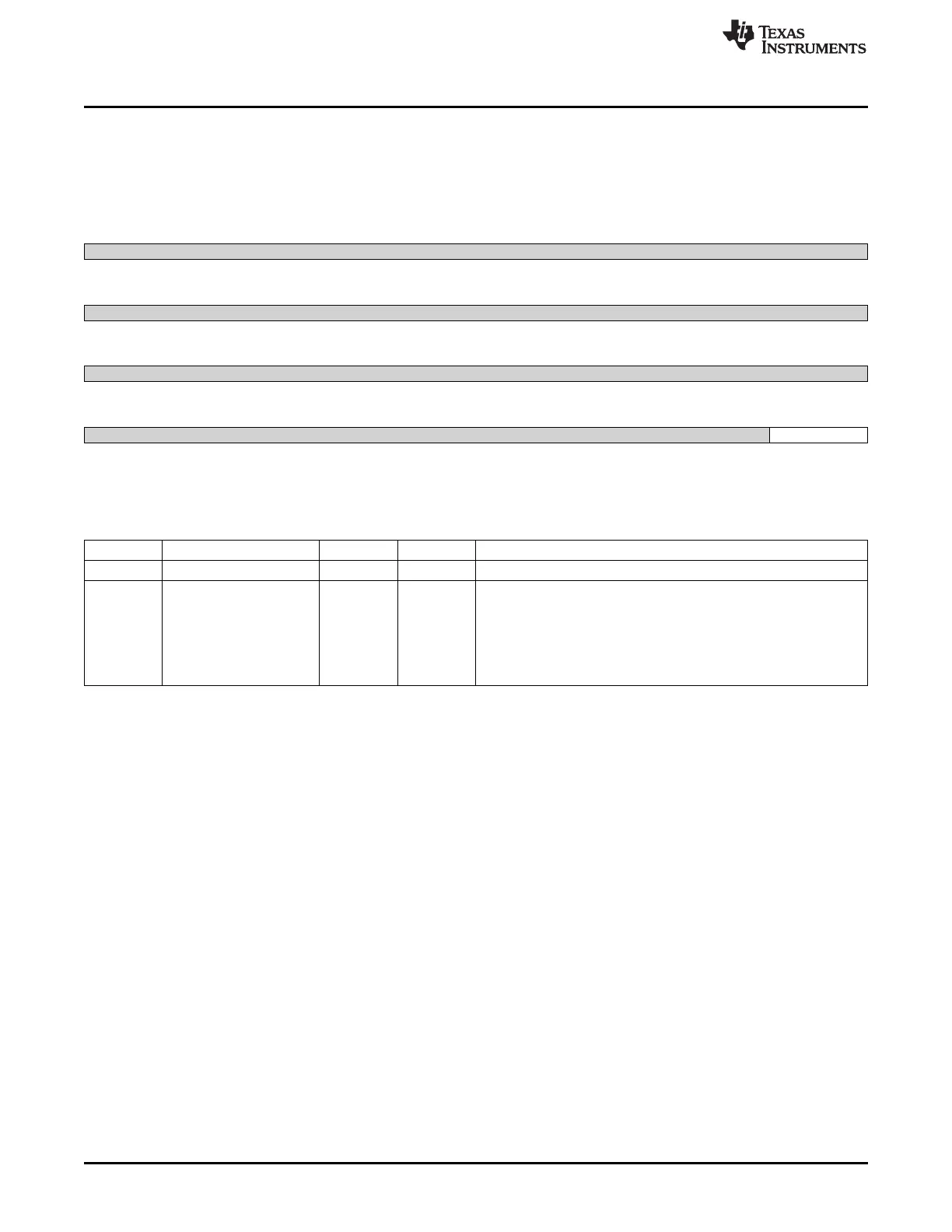

Table 14-98. CPTS_EVENT_POP Register Field Descriptions

Bit Field Type Reset Description

31-1 Reserved R 0h

0 EVENT_POP W 0h Event Pop - When a logic high is written to this bit an event is

popped off the event FIFO.

The event FIFO pop occurs as part of the interrupt process after the

event has been read in the Event_Low and Event_High registers.

Popping an event discards the event and causes the next event, if

any, to be moved to the top of the FIFO ready to be read by software

on interrupt.

1318

Ethernet Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...