Spinlock

www.ti.com

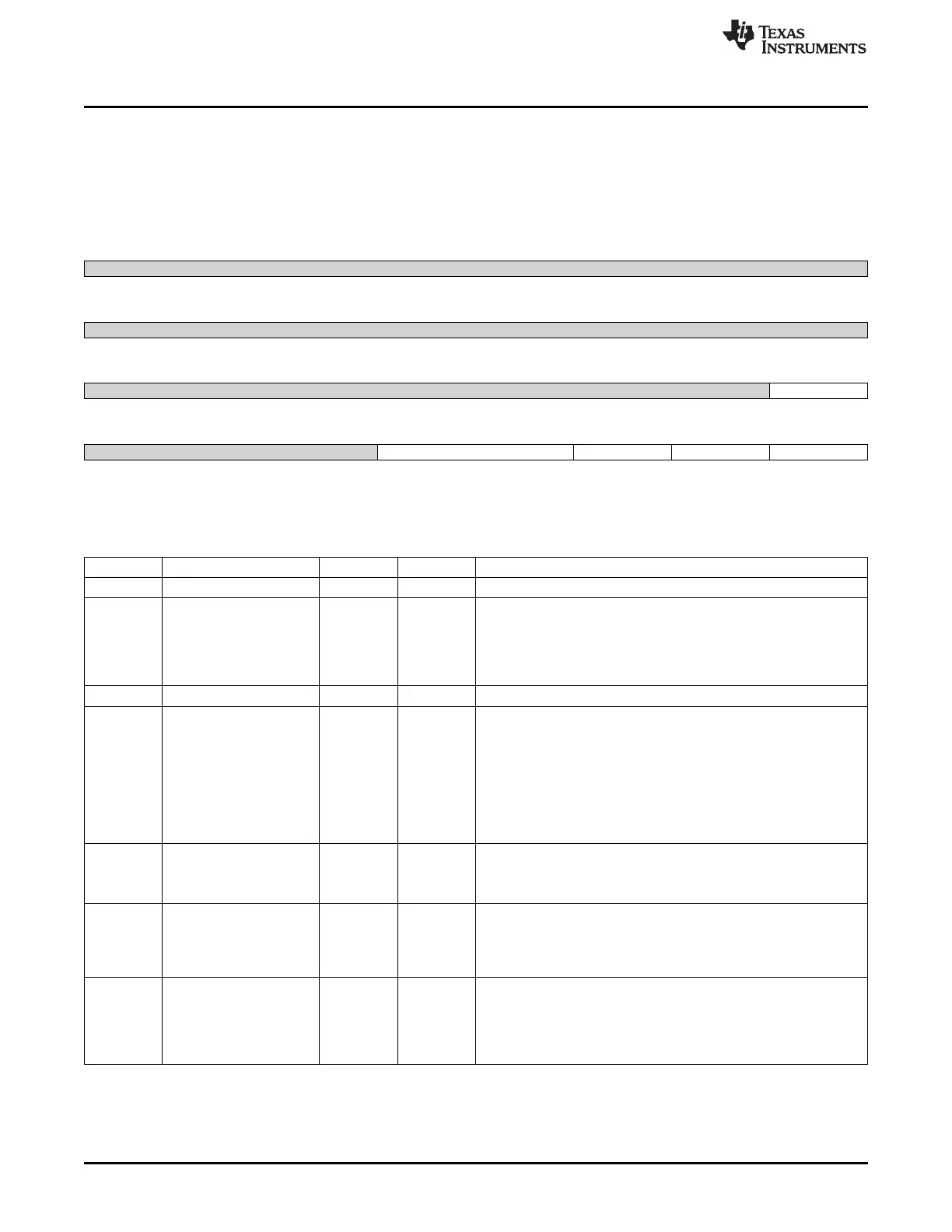

17.2.1.2 SYSCONFIG Register (offset = 10h) [reset = 11h]

SYSCONFIG is shown in Figure 17-46 and described in Table 17-59.

This register controls the various parameters of the OCP interface. Note that several fields are present by

read-only.

Figure 17-46. SYSCONFIG Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved CLOCKACTIVITY

R-0h R-0h

7 6 5 4 3 2 1 0

Reserved SIDLEMODE ENWAKEUP SOFTRESET AUTOGATING

R-0h R-2h R-4h W-8h R-11h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

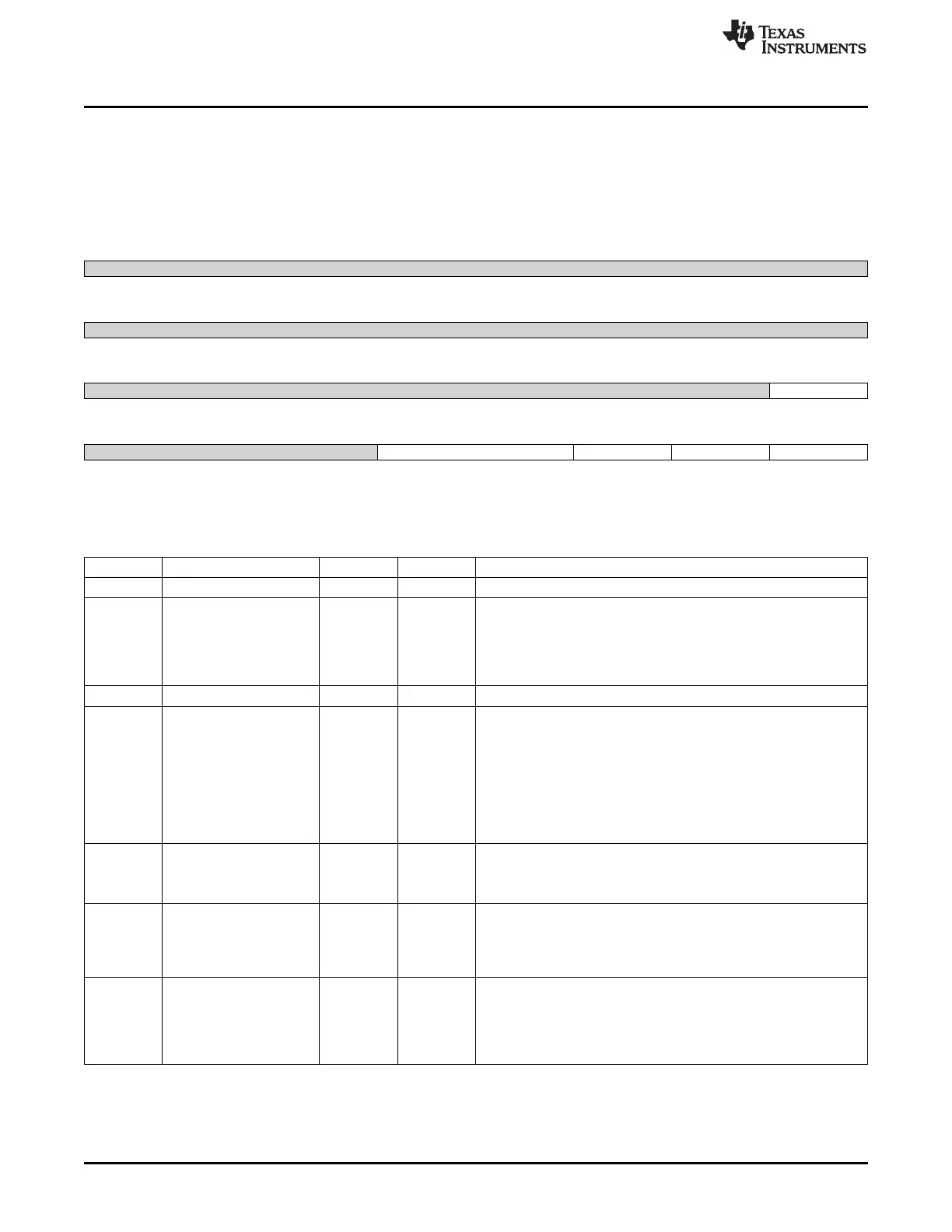

Table 17-59. SYSCONFIG Register Field Descriptions

Bit Field Type Reset Description

31-9 Reserved R 0h

8 CLOCKACTIVITY R 0h

Indicates whether the module requires the OCP when in IDLE mode.

0 = NOTREQUIRED : OCP clock is not required by the module

during IDLE mode and may be switched off.

1 = REQUIRED : OCP clock is required by the module, even during

idle mode.

7-5 Reserved R 0h

4-3 SIDLEMODE R 2h

Control of the slave interface power management IDLE request

acknowledgement.

0 = FORCEIDLE : IDLE request is acknowledged unconditionally

and immediately.

1 = NOIDLE : IDLE request is never acknowledged.

2 = SMARTIDLE : IDLE request acknowledgement is based on the

internal module activity.

3 = unused3 : Reserved. Do not use.

2 ENWAKEUP R 4h

Asynchronous wakeup gereration.

0 = NOWAKEUPGEN : Wakeup generation is disabled.

1 = WAKEUPGEN1 : Enable wakeup generation.

1 SOFTRESET W 8h

Module software reset.

0 = NOOP : No Description

1 = DORESET : Start a soft reset sequence of the Spin Lock

module.

0 AUTOGATING R 11h

Internal OCP clock gating strategy.

0 = FREERUNNING : OCP clock is not gated when OCP interface is

idle.

1 = GATED : Automatic internal OCP clock gating strategy is

applied, based on the OCP interface activity.

3310

Interprocessor Communication SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...