www.ti.com

EMIF

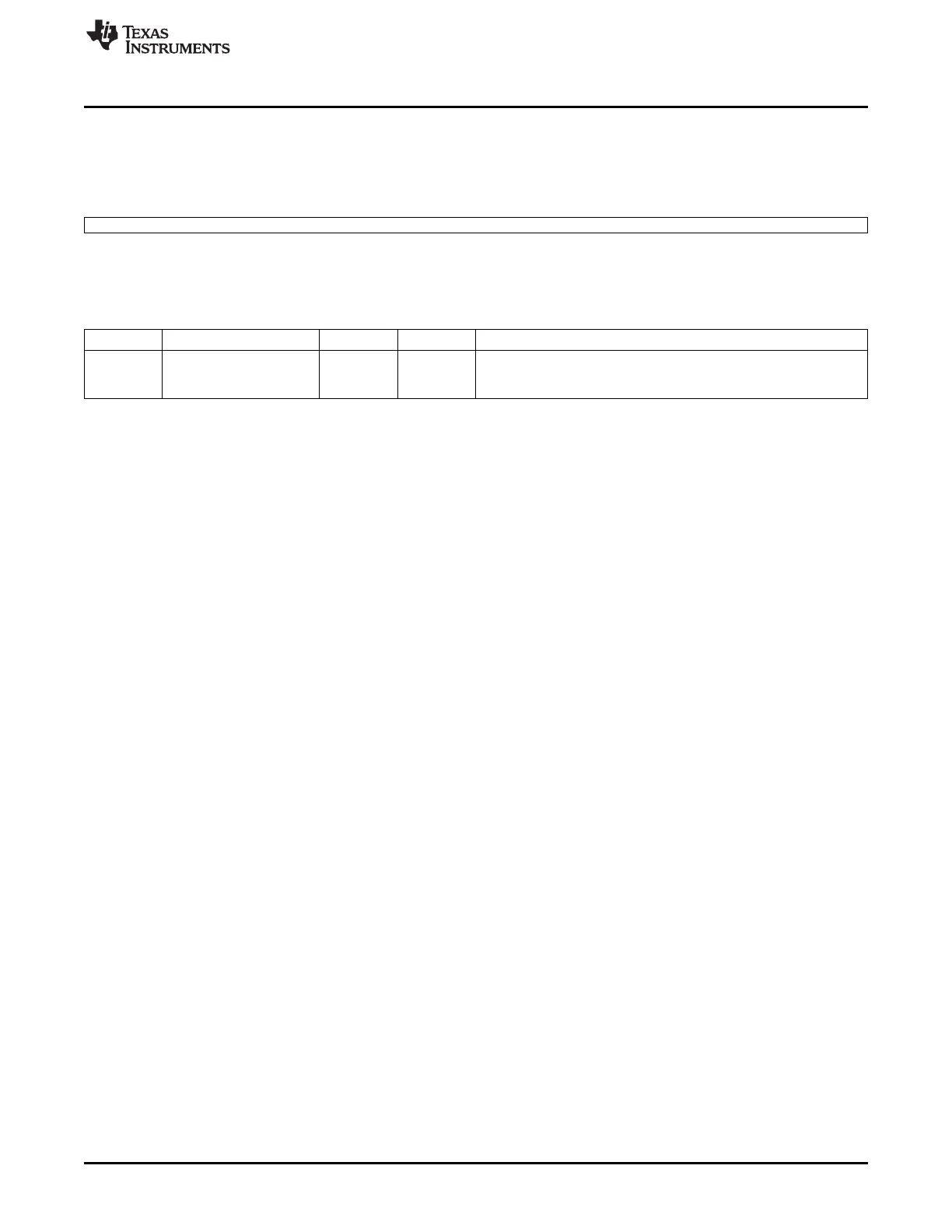

7.3.5.18 PERF_CNT_1 Register (offset = 80h) [reset = 0h]

PERF_CNT_1 is shown in Figure 7-108 and described in Table 7-128.

Figure 7-108. PERF_CNT_1 Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reg_counter1

R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

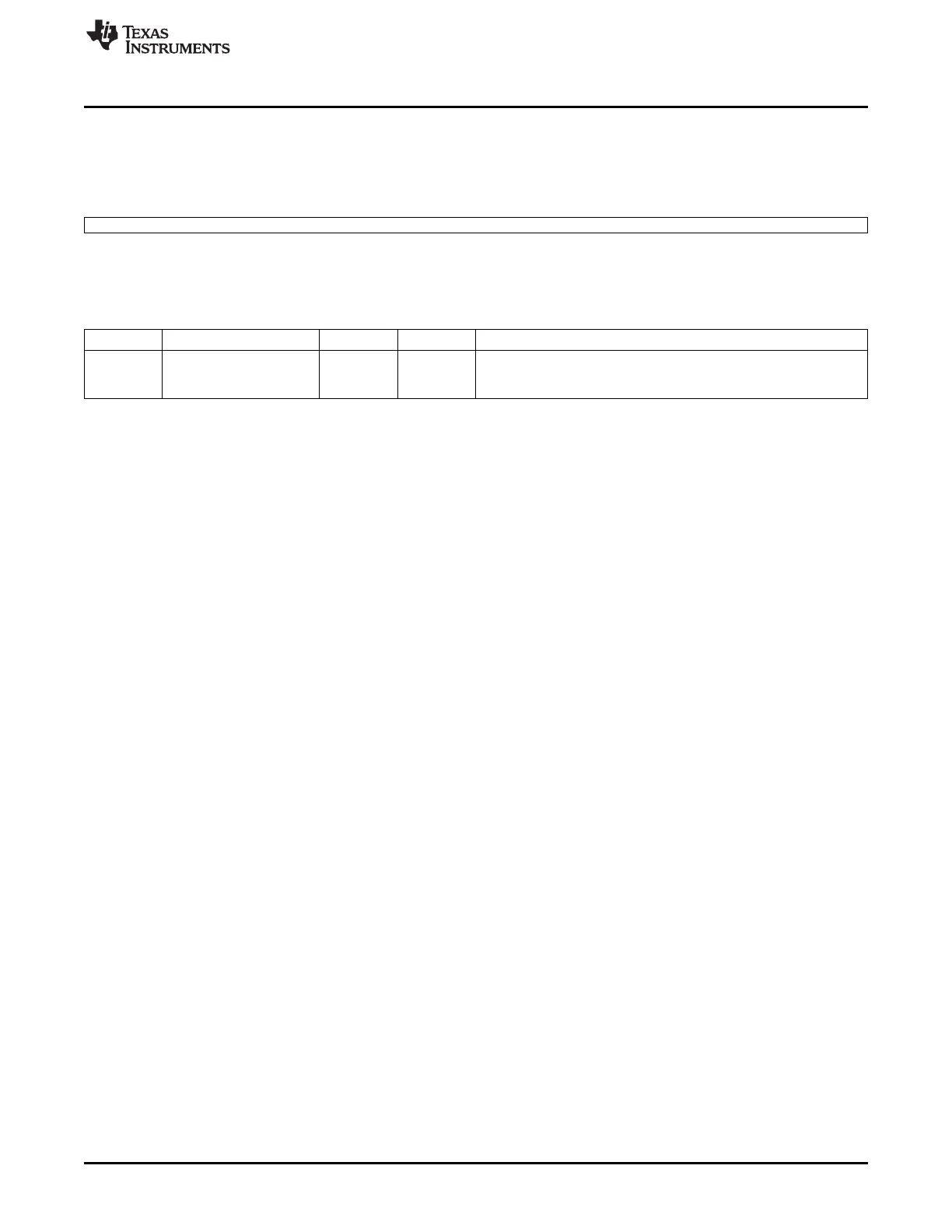

Table 7-128. PERF_CNT_1 Register Field Descriptions

Bit Field Type Reset Description

31-0 reg_counter1 R 0h 32-bit counter that can be configured as specified in the

Performance Counter Config Register and Performance Counter

Master Region Select Register.

443

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...