www.ti.com

UART Registers

19.5.1.37 Enhanced Feature Register (EFR)

The enhanced feature register (EFR) enables or disables enhanced features. Most enhanced functions

apply only to UART modes, but EFR[4] enables write accesses to FCR[5:4], the TX trigger level, which is

also used in IrDA modes. The enhanced feature register (EFR) is shown in Figure 19-70 and described in

Table 19-68.

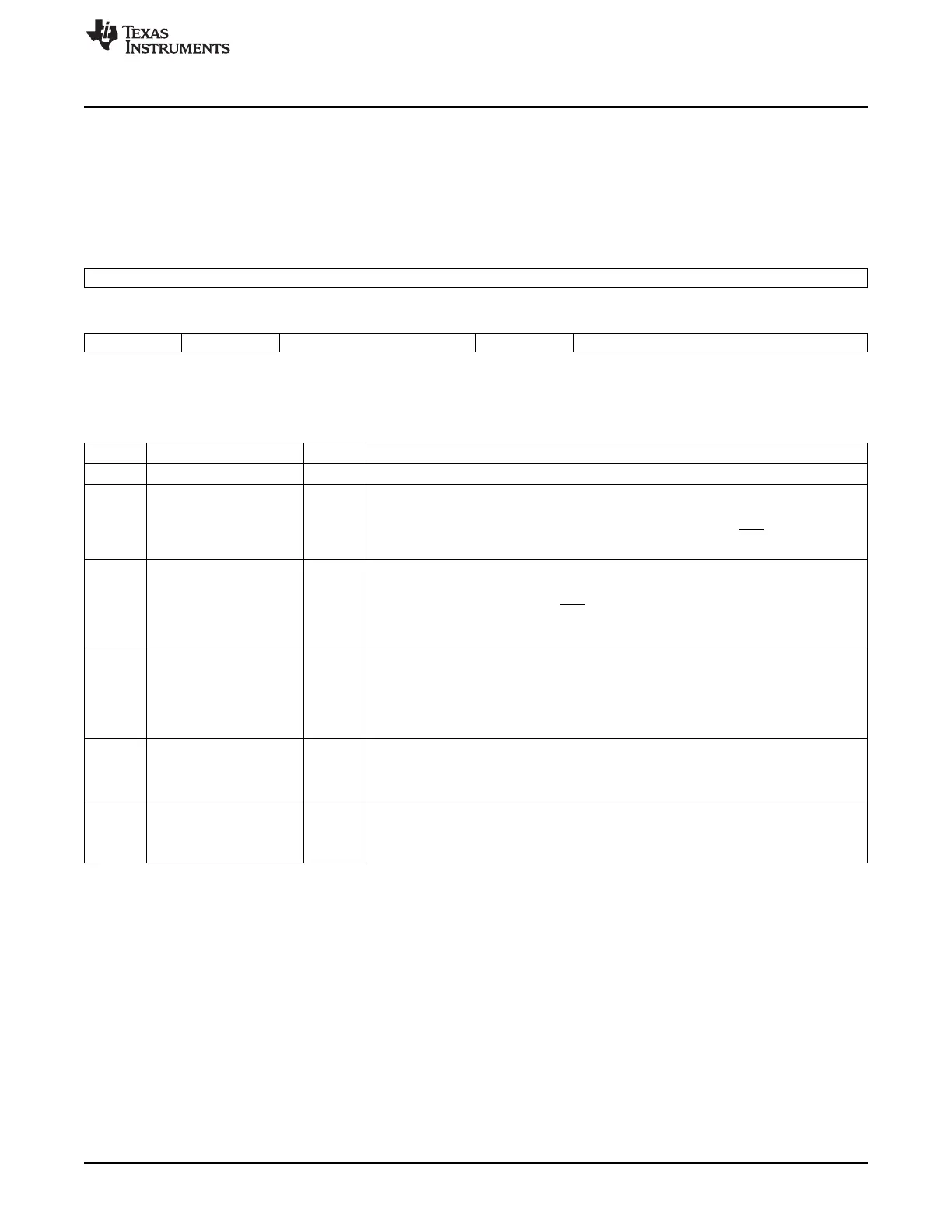

Figure 19-70. Enhanced Feature Register (EFR)

15 8

Reserved

R-0

7 6 5 4 3 0

AUTOCTSEN AUTORTSEN SPECIALCHARDETECT ENHANCEDEN SWFLOWCONTROL

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

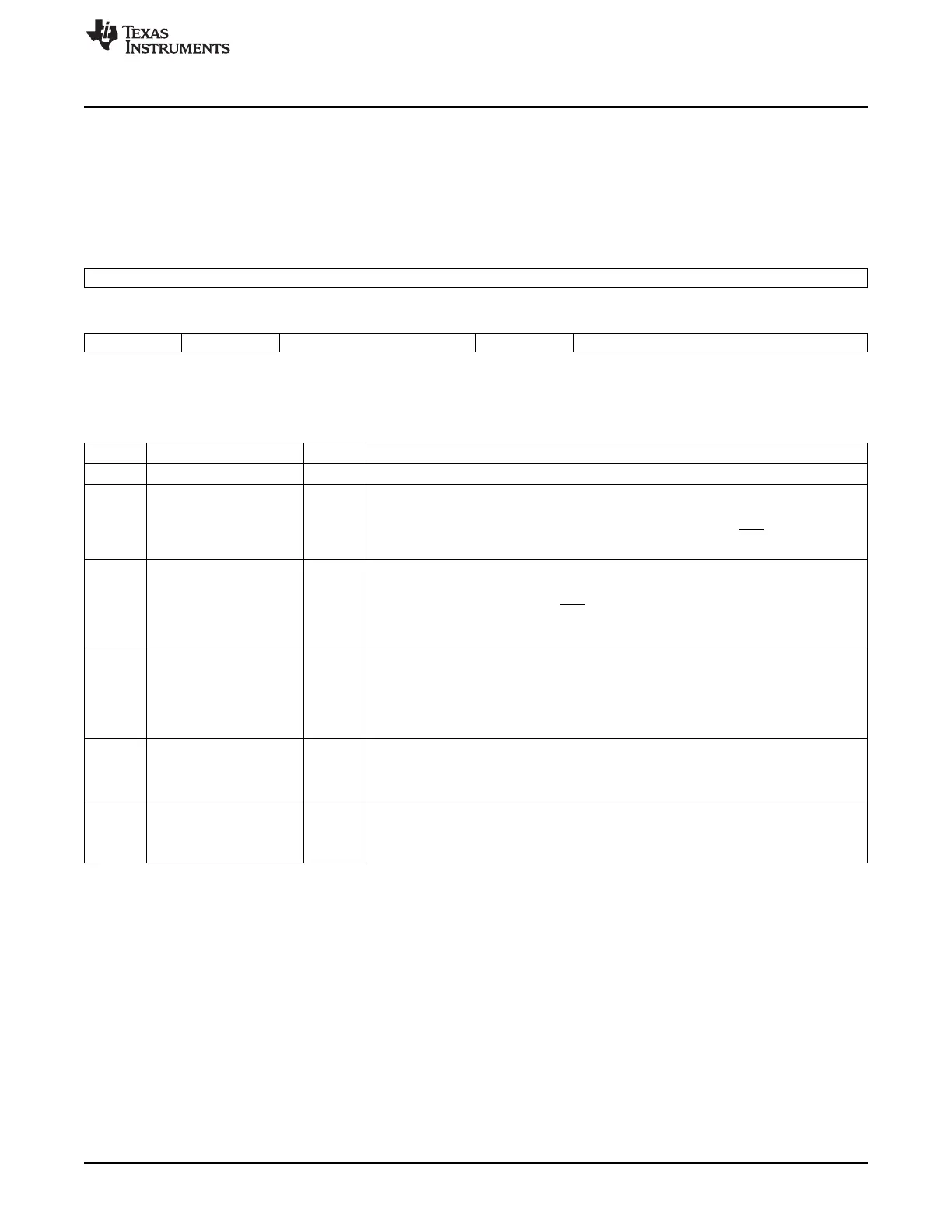

Table 19-68. Enhanced Feature Register (EFR) Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7 AUTOCTSEN Auto-CTS enable bit (UART mode only).

0 Normal operation.

1 Auto-CTS flow control is enabled; transmission is halted when the CTS pin is high

(inactive).

6 AUTORTSEN Auto-RTS enable bit (UART mode only).

0 Normal operation.

1 Auto-RTS flow control is enabled; RTS pin goes high (inactive) when the receiver FIFO

HALT trigger level, TCR[3:0], is reached and goes low (active) when the receiver FIFO

RESTORE transmission trigger level is reached.

5 SPECIALCHARDETECT Special character detect (UART mode only).

0 Normal operation.

1 Special character detect enable. Received data is compared with XOFF2 data. If a

match occurs, the received data is transferred to RX FIFO and the IIR[4] bit is set to 1 to

indicate that a special character was detected.

4 ENHANCEDEN Enhanced functions write enable bit.

0 Disables writing to IER[7:4], FCR[5:4], and MCR[7:5].

1 Enables writing to IER[7:4], FCR[5:4], and MCR[7:5].

3-0 SWFLOWCONTROL 0-Fh Combinations of software flow control can be selected by programming this bit. XON1

and XON2 should be set to different values if the software flow control is enabled. See

Table 19-69. In IrDA mode, EFR[1:0] selects the IR address to check. See IR Address

Checking.

3537

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...