www.ti.com

GPMC

7.1.5.26 GPMC_ECC_CONTROL

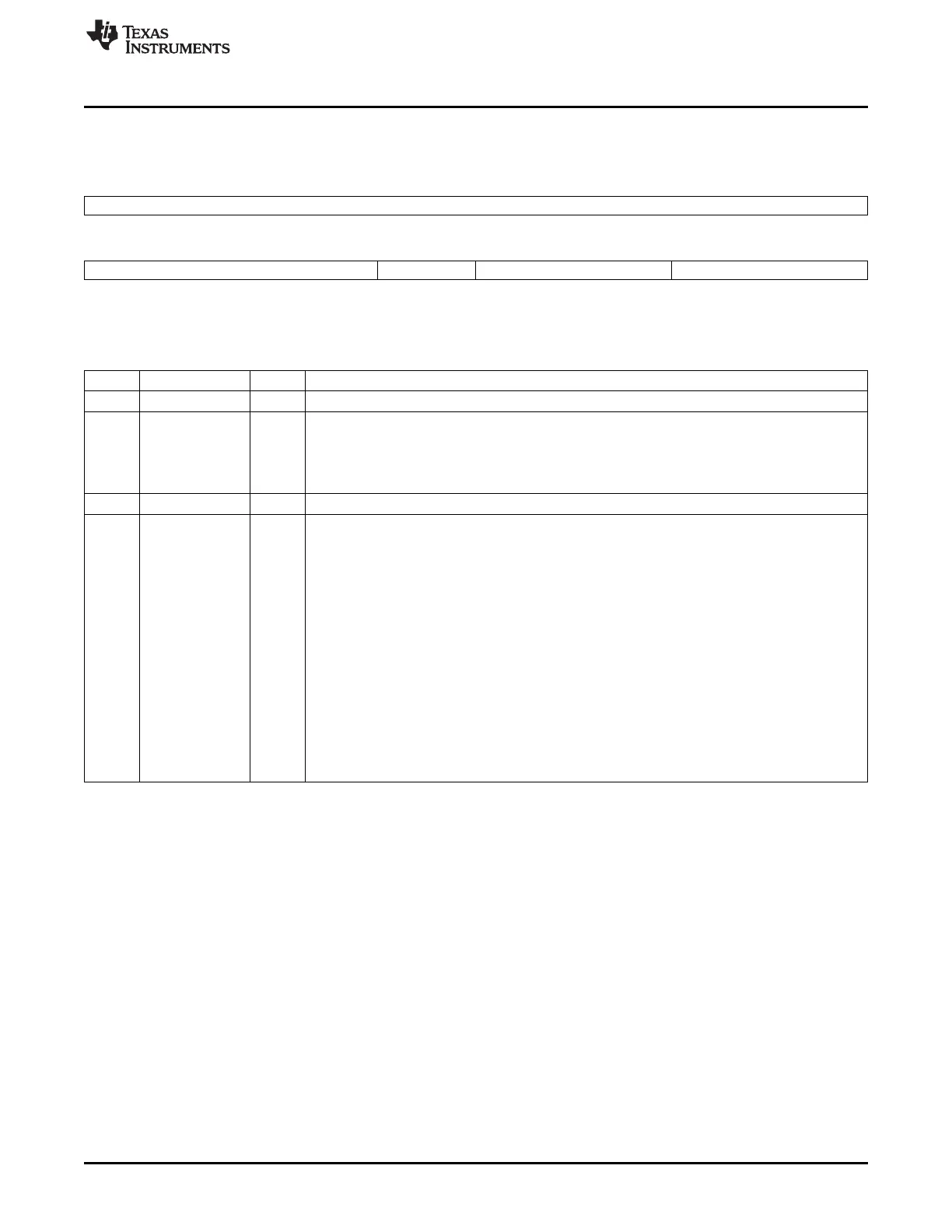

Figure 7-76. GPMC_ECC_CONTROL

31 16

Reserved

R-0

15 9 8 7 4 3 0

Reserved ECCCLEAR Reserved ECCPOINTER

R-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

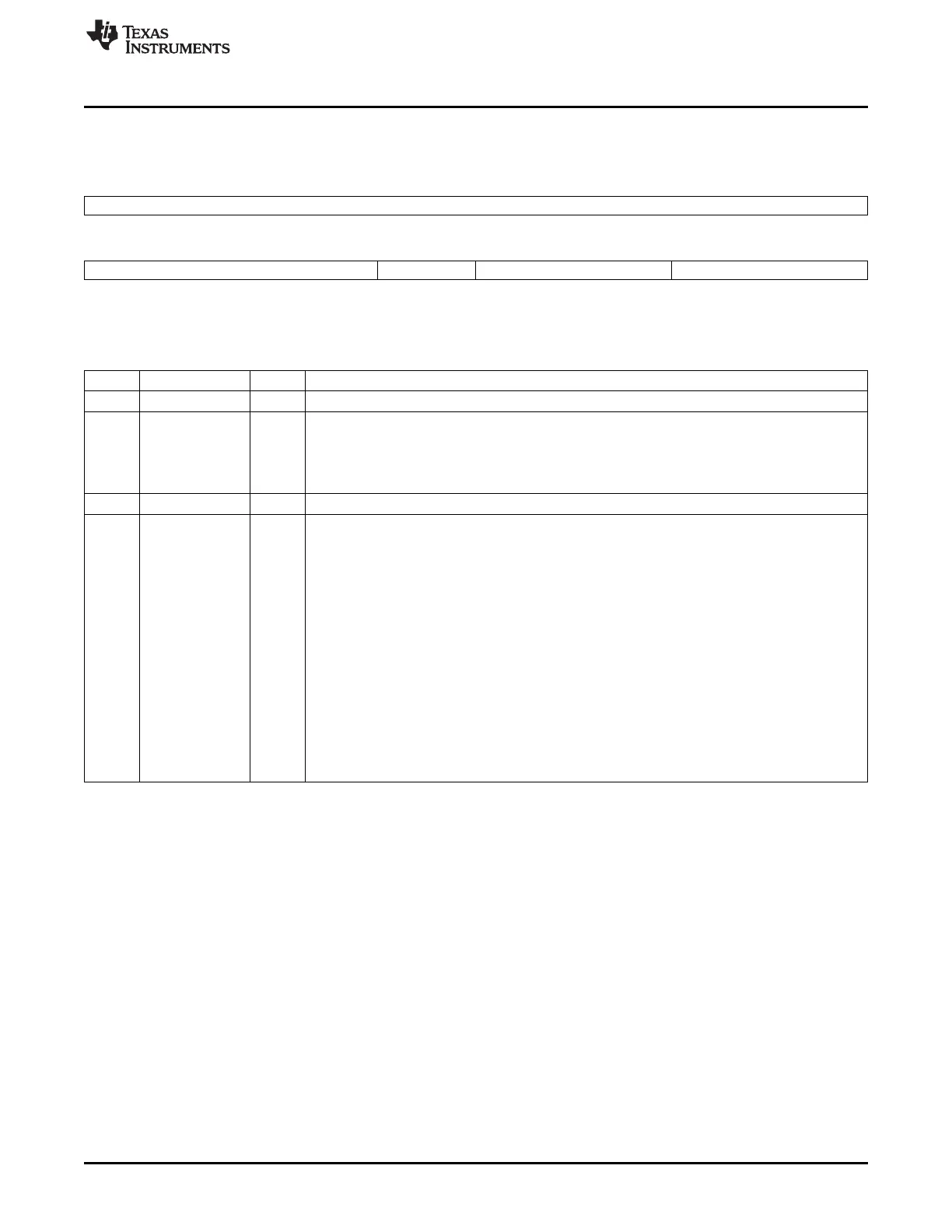

Table 7-80. GPMC_ECC_CONTROL Field Descriptions

Bit Field Value Description

31-9 Reserved 0 Reserved

8 ECCCLEAR Clear all ECC result registers

R0 All reads return 0

W0 Ignored

W1 Clears all ECC result registers

7-4 Reserved 0 Reserved

3-0 ECCPOINTER 0-Fh Selects ECC result register (Reads to this field give the dynamic position of the ECC pointer -

Writes to this field select the ECC result register where the first ECC computation will be stored).

Writing values not listed disables the ECC engine (ECCEnable bit of GPMC_ECC_CONFIG cleared

to 0).

0 Writing 0 disables the ECC engine (ECCENABLE bit of GPMC_ECC_CONFIG cleared to 0)

1h ECC result register 1 selected

2h ECC result register 2 selected

3h ECC result register 3 selected

4h ECC result register 4 selected

5h ECC result register 5 selected

6h ECC result register 6 selected

7h ECC result register 7 selected

8h ECC result register 8 selected

9h ECC result register 9 selected

391

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...