Multimedia Card Registers

www.ti.com

18.5.1.26 SD_ADMAES Register (offset = 254h) [reset = 0h]

SD_ADMAES is shown in Figure 18-62 and described in Table 18-45.

When an ADMA Error Interrupt has occurred, the ADMA Error States field in this register holds the ADMA

state and the ADMA System Address Register holds the address around the error descriptor. For

recovering the error, the Host Driver requires the ADMA state to identify the error descriptor address as

follows: ST_STOP: Previous location set in the ADMA System Address register is the error descriptor

address. ST_FDS: Current location set in the ADMA System Address register is the error descriptor

address. ST_CADR: This sate is never set because do not generate ADMA error in this state. ST_TFR:

Previous location set in the ADMA System Address register is the error descriptor address. In the case of

a write operation, the Host Driver should use ACMD22 to get the number of written block rather than using

this information, since unwritten data may exist in the Host Controller. The Host Controller generates the

ADMA Error Interrupt when it detects invalid descriptor data (Valid = 0) at the ST_FDS state. In this case,

ADMA Error State indicates that an error occurs at ST_FDS state. The Host Driver may find that the Valid

bit is not set in the error descriptor.

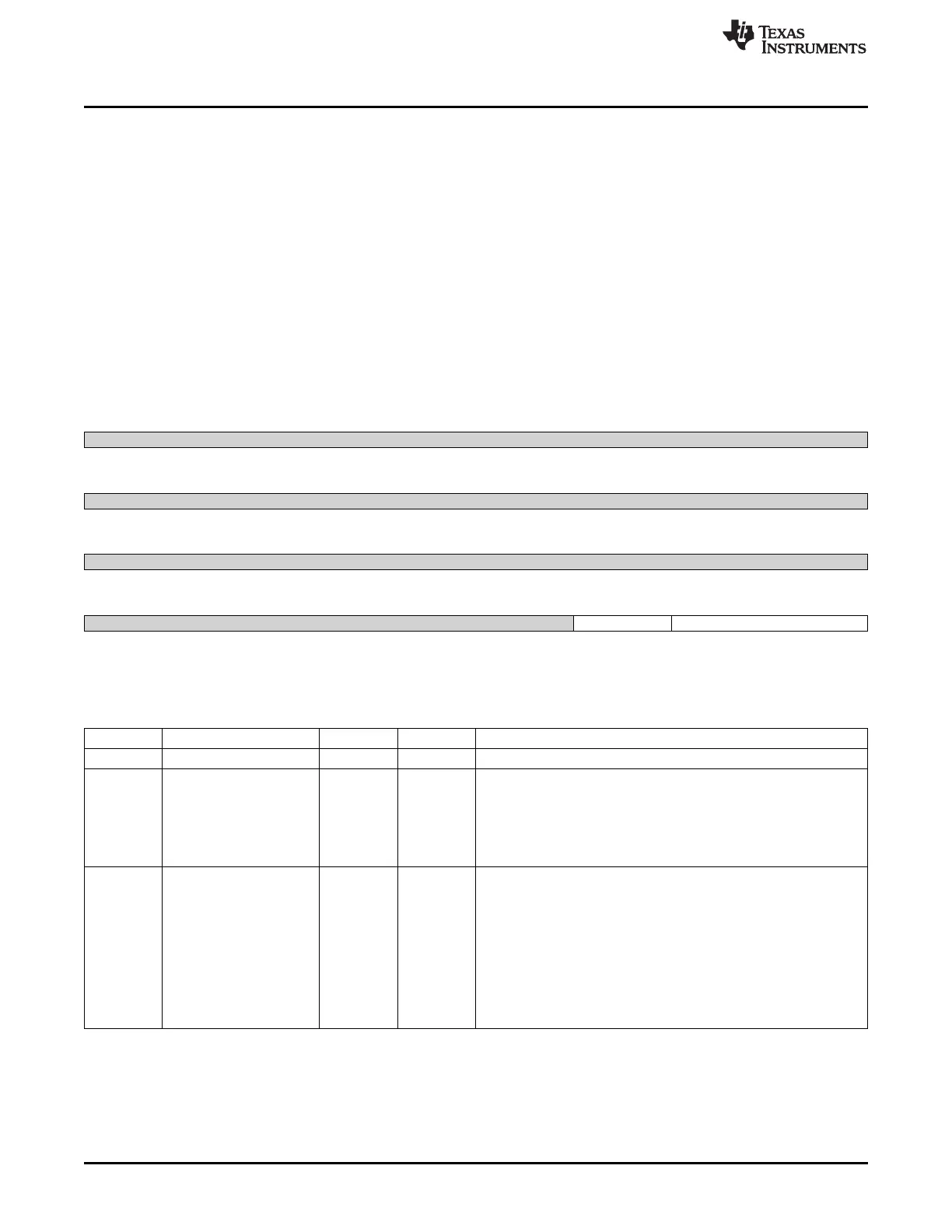

Figure 18-62. SD_ADMAES Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved LME AES

R-0h W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

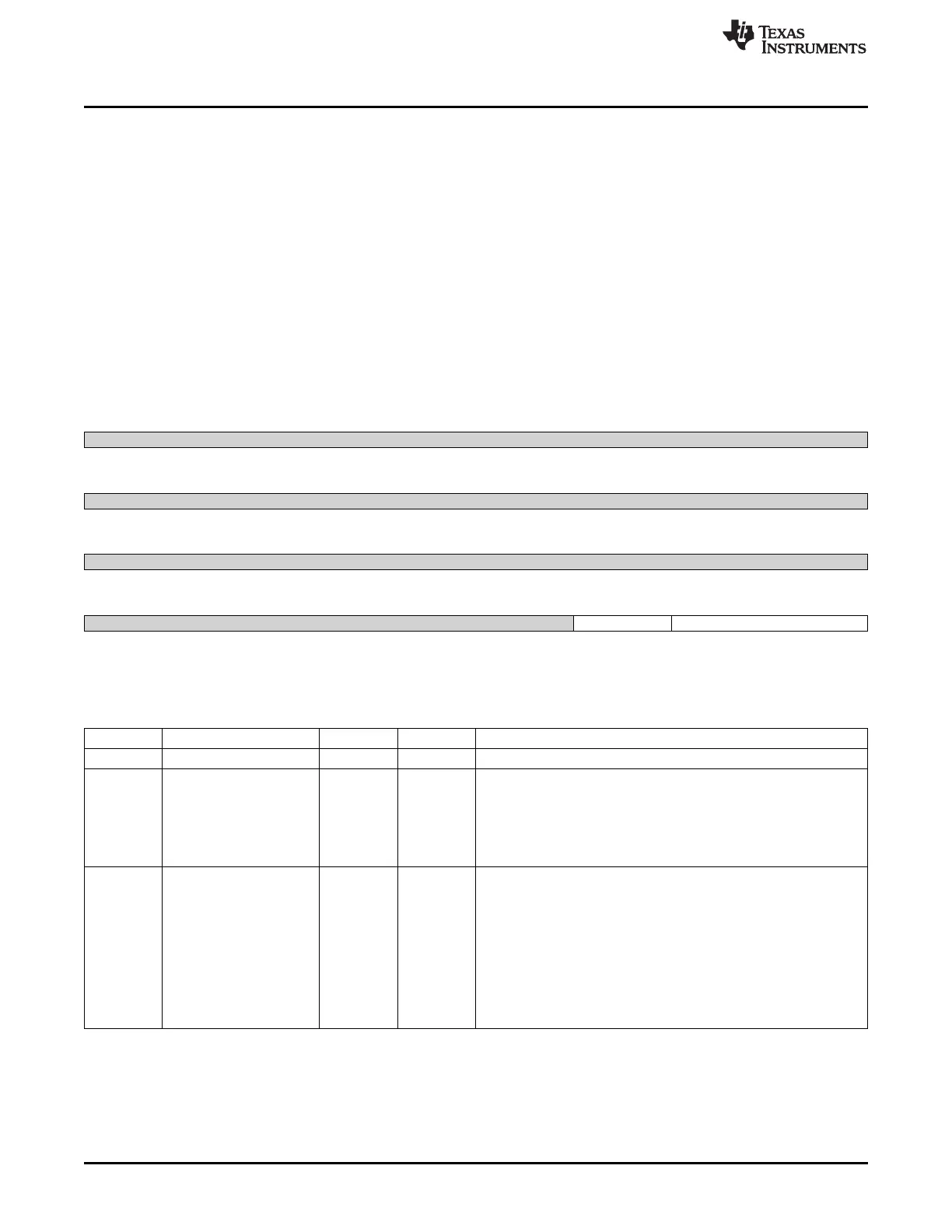

Table 18-45. SD_ADMAES Register Field Descriptions

Bit Field Type Reset Description

31-3 Reserved R 0h

2 LME W 0h ADMA Length Mismatch Error: While Block Count Enable is being

set, the total data length specified by the Descriptor table is different

from that specified by the Block Count and Block Length.

Total data length cannot be divided by the block length.

0x0 = No error

0x1 = Error

1-0 AES R/W 0h ADMA Error State.

This field indicates the state of ADMA when an error occurred during

an ADMA data transfer.

This field never indicates "10" because ADMA never stops in this

state.

0x0(R) = ST_STOP (Stop DMA). Contents of the SYS_SDR register

0x1(W) = ST_STOP (Stop DMA). Points to the error descriptor.

0x2(R) = Never set this state. (Not used)

0x3(W) = ST_TFR (Transfer Data). Points to the 'next' of the error

descriptor.

3442

Multimedia Card (MMC) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...