www.ti.com

CONTROL_MODULE Registers

9.3.65 tpcc_evt_mux_36_39 Register (offset = FB4h) [reset = 0h]

tpcc_evt_mux_36_39 is shown in Figure 9-68 and described in Table 9-75.

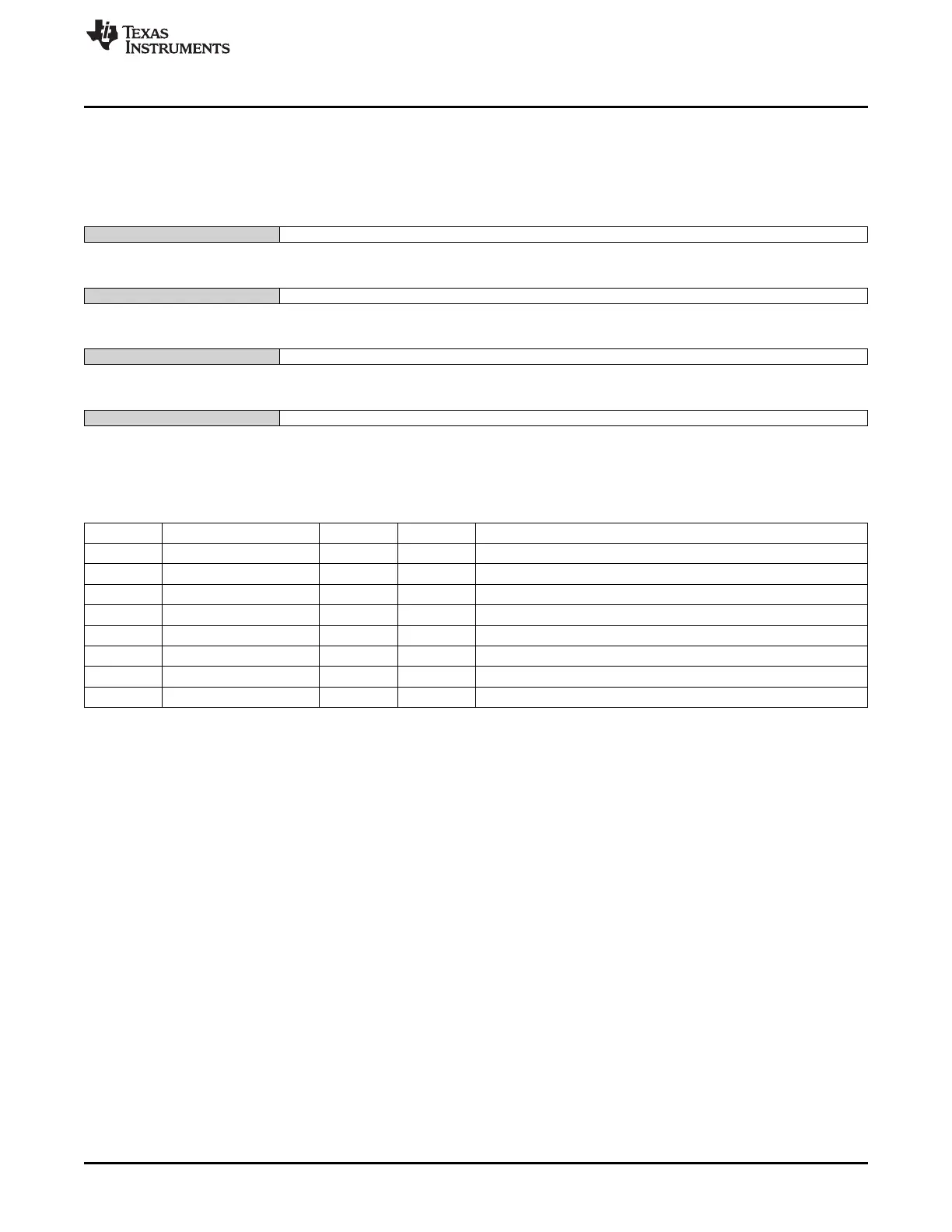

Figure 9-68. tpcc_evt_mux_36_39 Register

31 30 29 28 27 26 25 24

Reserved evt_mux_39

R-0h R/W-0h

23 22 21 20 19 18 17 16

Reserved evt_mux_38

R-0h R/W-0h

15 14 13 12 11 10 9 8

Reserved evt_mux_37

R-0h R/W-0h

7 6 5 4 3 2 1 0

Reserved evt_mux_36

R-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

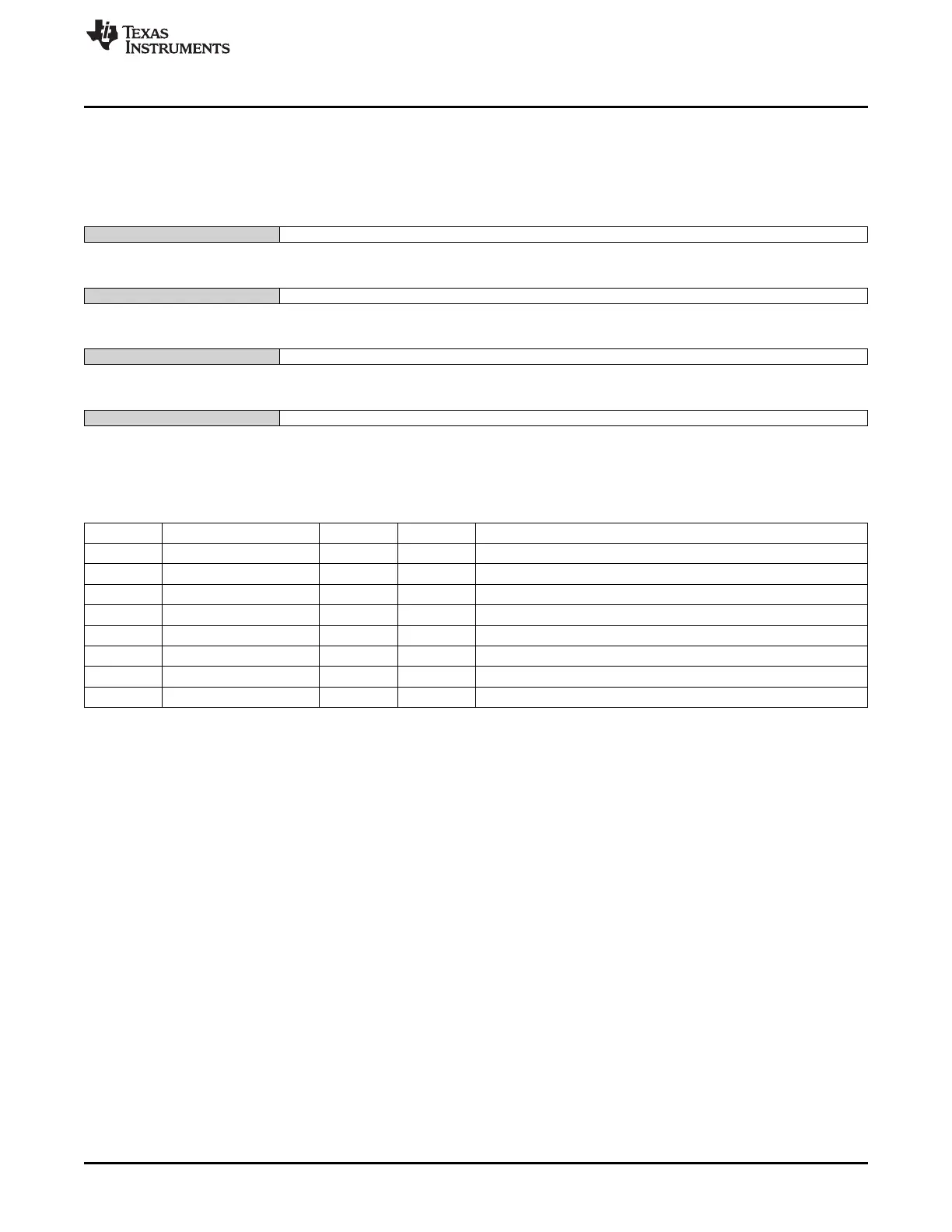

Table 9-75. tpcc_evt_mux_36_39 Register Field Descriptions

Bit Field Type Reset Description

31-30 Reserved R 0h

29-24 evt_mux_39 R/W 0h Selects 1 of 64 inputs for DMA event 39

23-22 Reserved R 0h

21-16 evt_mux_38 R/W 0h Selects 1 of 64 inputs for DMA event 38

15-14 Reserved R 0h

13-8 evt_mux_37 R/W 0h Selects 1 of 64 inputs for DMA event 37

7-6 Reserved R 0h

5-0 evt_mux_36 R/W 0h Selects 1 of 64 inputs for DMA event 36

829

SPRUH73H–October 2011–Revised April 2013 Control Module

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...