UART Registers

www.ti.com

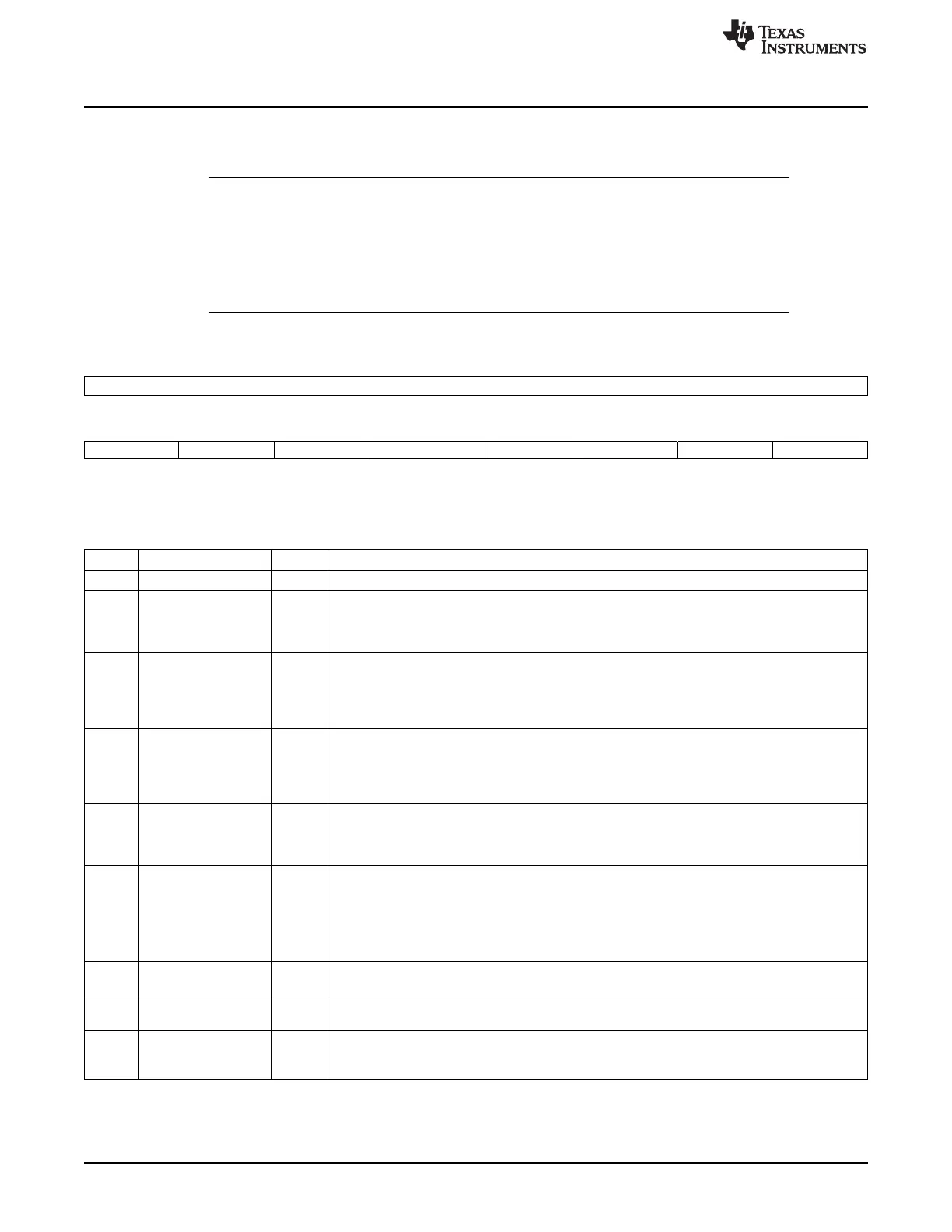

19.5.1.26 Auxiliary Control Register (ACREG)

The auxiliary control register (ACREG) is shown in Figure 19-59 and described in Table 19-57.

NOTE:

• If transmit FIFO is not empty and MDR1[5] = 1, IrDA starts a new transfer with data of

previous frame as soon as abort frame has been sent. Therefore, TX FIFO must be

reset before sending an abort frame.

• It is recommended to disable TX FIFO underrun capability by masking corresponding

underrun interrupt. When disabling underrun by setting ACREG[4] = 1, unknown data is

sent over TX line.

Figure 19-59. Auxiliary Control Register (ACREG)

15 8

Reserved

R-0

7 6 5 4 3 2 1 0

PULSETYPE SDMOD DISIRRX DISTXUNDERRUN SENDSIP SCTXEN ABORTEN EOTEN

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

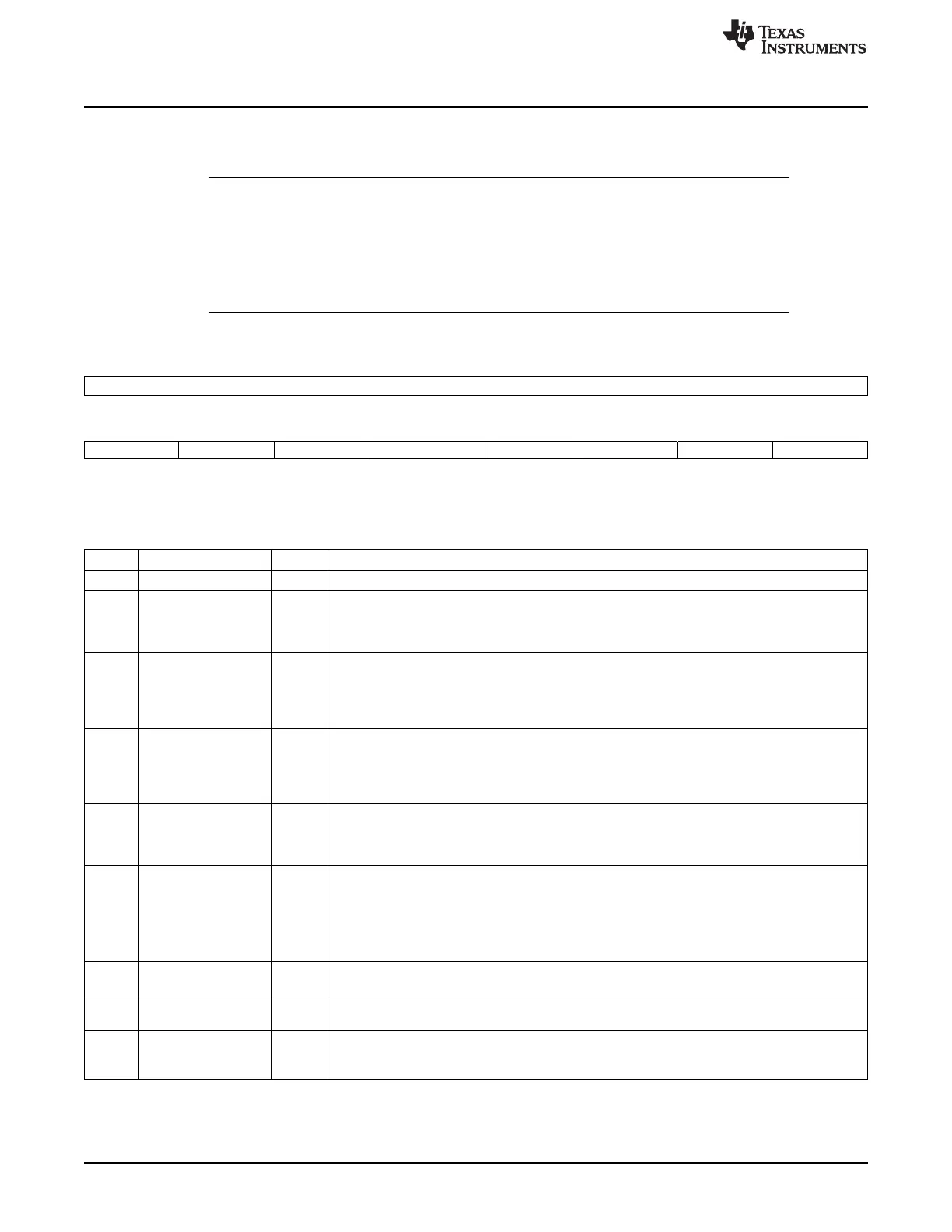

Table 19-57. Auxiliary Control Register (ACREG) Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7 PULSETYPE SIR pulse-width select:

0 3/16 of baud-rate pulse width

1 1.6 μs

6 SDMOD Primary output used to configure transceivers. Connected to the SD/MODE input pin of IrDA

transceivers.

0 SD pin is set to high.

1 SD pin is set to low.

5 DISIRRX Disable RX input.

0 Normal operation (RX input automatically disabled during transmit, but enabled outside of

transmit operation).

1 Disables RX input (permanent state; independent of transmit).

4 DISTXUNDERRUN Disable TX underrun.

0 Long stop bits cannot be transmitted. TX underrun is enabled.

1 Long stop bits can be transmitted.

3 SENDSIP MIR/FIR modes only. Send serial infrared interaction pulse (SIP).

If this bit is set during an MIR/FIR transmission, the SIP is sent at the end of it. This bit is

automatically cleared at the end of the SIP transmission.

0 No action.

1 Send SIP pulse.

2 SCTXEN Store and control TX start. When MDR1[5] = 1 and the LH writes 1 to this bit, the TX state-

machine starts frame transmission. This bit is self-clearing.

1 ABORTEN Frame abort. The LH can intentionally abort transmission of a frame by writing 1 to this bit.

Neither the end flag nor the CRC bits are appended to the frame.

0 EOTEN EOT (end-of-transmission) bit. The LH writes 1 to this bit just before it writes the last byte to the

TX FIFO in the set-EOT bit frame-closing method. This bit is automatically cleared when the LH

writes to the THR (TX FIFO).

3528

Universal Asynchronous Receiver/Transmitter (UART) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...