EMIF

www.ti.com

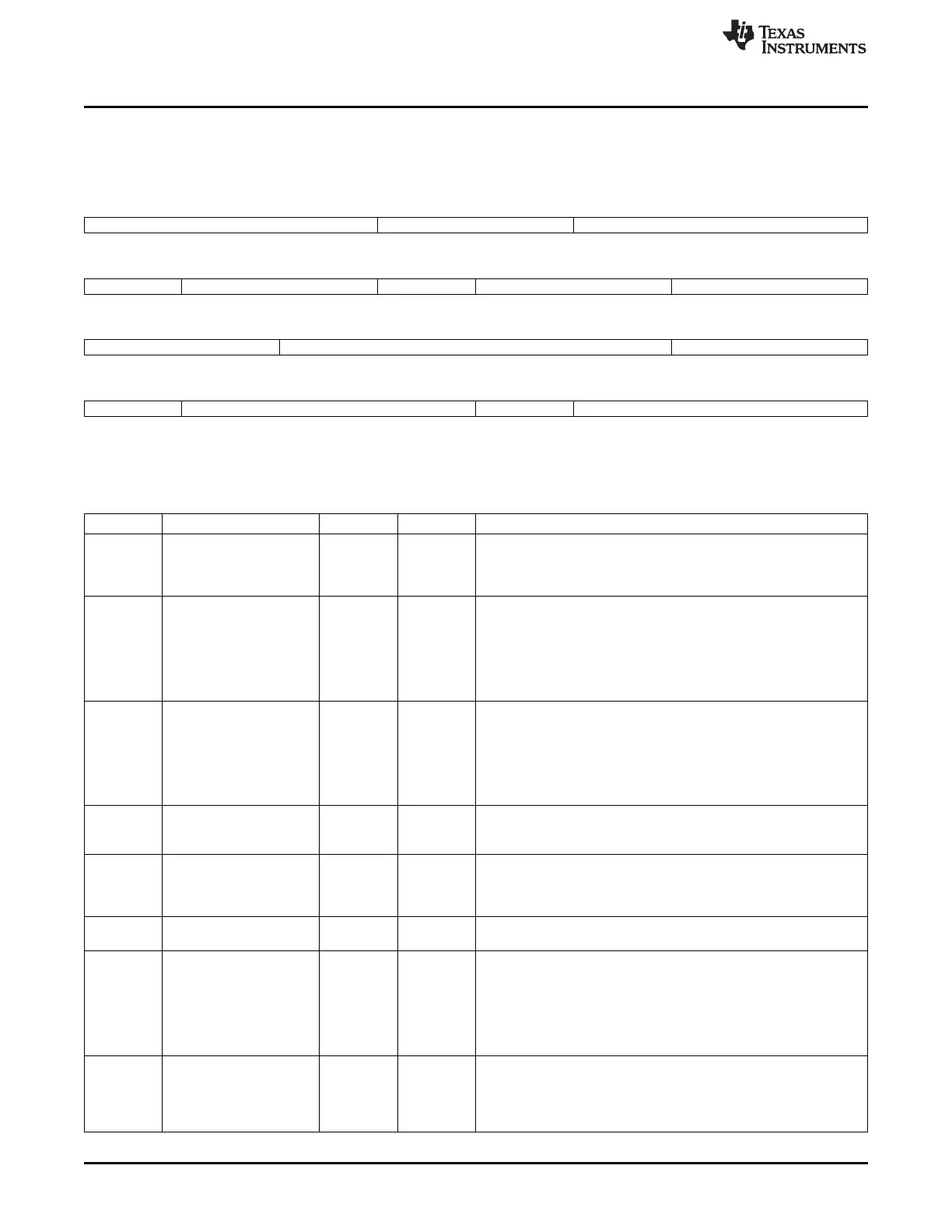

7.3.5.3 SDRAM_CONFIG Register (offset = 8h) [reset = 0h]

SDRAM_CONFIG is shown in Figure 7-93 and described in Table 7-113.

Figure 7-93. SDRAM_CONFIG Register

31 30 29 28 27 26 25 24

reg_sdram_type reg_ibank_pos reg_ddr_term

R/W-0h R/W-0h R/W-0h

23 22 21 20 19 18 17 16

reg_ddr2_ddqs reg_dyn_odt reg_ddr_disable_dll reg_sdram_drive reg_cwl

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

15 14 13 12 11 10 9 8

reg_narrow_mode reg_cl reg_rowsize

R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

reg_rowsize reg_ibank reg_ebank reg_pagesize

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

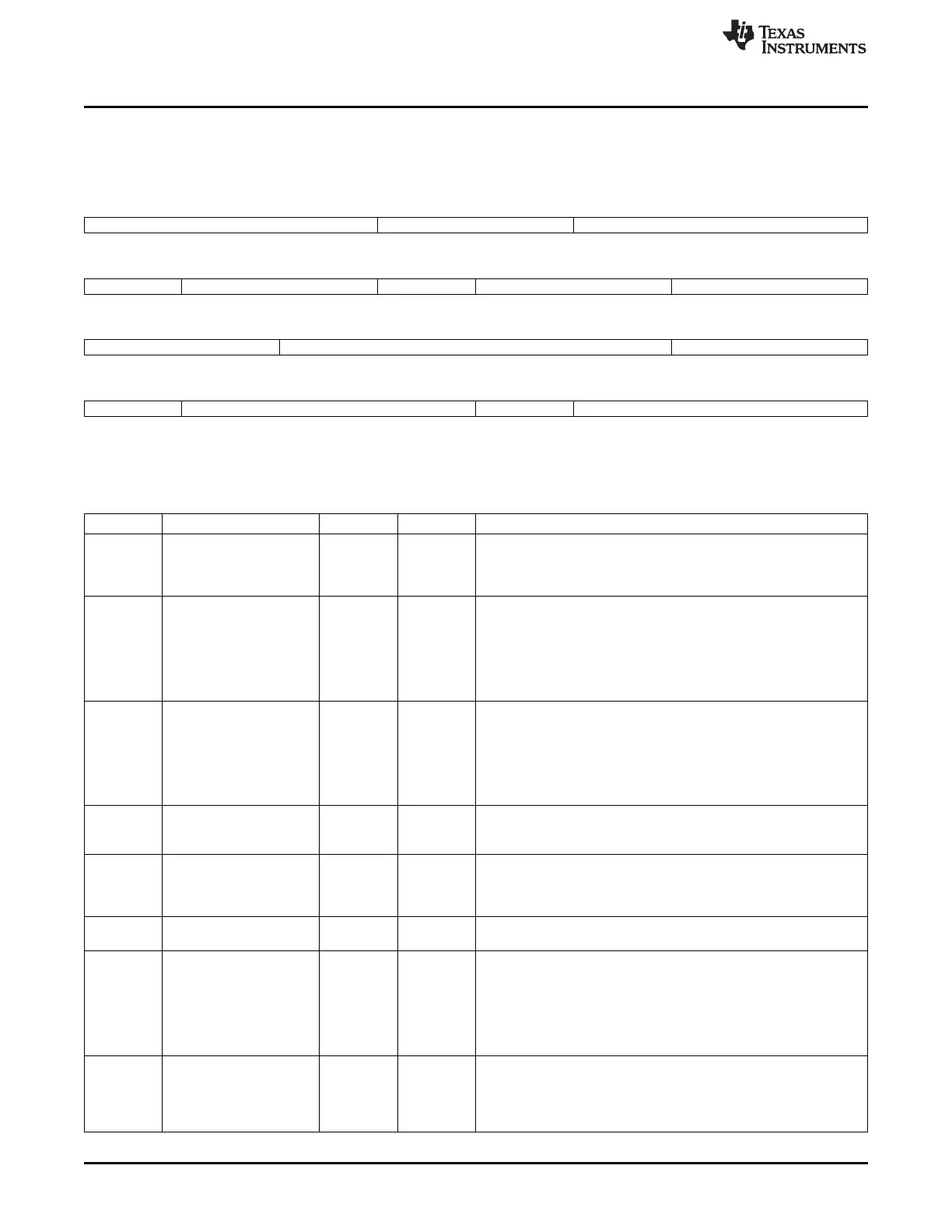

Table 7-113. SDRAM_CONFIG Register Field Descriptions

Bit Field Type Reset Description

31-29 reg_sdram_type R/W 0h SDRAM Type selection.

Set to 0 for DDR1, set to 1 for LPDDR1, set to 2 for DDR2, set to 3

for DDR3.

All other values are reserved.

28-27 reg_ibank_pos R/W 0h Internal bank position.

Set to 0 to assign internal bank address bits from lower OCP

address bits, as shown in the tables for OCP Address to

DDR2/3/mDDR Address Mapping.

Set to 1, 2, or 3 to assign internal bank address bits from higher

OCP address, as shown in the tables for OCP Address to

DDR2/3/mDDR Address Mapping.

26-24 reg_ddr_term R/W 0h DDR2 and DDR3 termination resistor value.

Set to 0 to disable termination.

For DDR2, set to 1 for 75 ohm, set to 2 for 150 ohm, and set to 3 for

50 ohm.

For DDR3, set to 1 for RZQ/4, set to 2 for RZQ/2, set to 3 for RZQ/6,

set to 4 for RZQ/12, and set to 5 for RZQ/8.

All other values are reserved.

23 reg_ddr2_ddqs R/W 0h DDR2 differential DQS enable.

Set to 0 for single ended DQS.

Set to 1 for differential DQS.

22-21 reg_dyn_odt R/W 0h DDR3 Dynamic ODT.

Set to 0 to turn off dynamic ODT.

Set to 1 for RZQ/4 and set to 2 for RZQ/2.

All other values are reserved.

20 reg_ddr_disable_dll R/W 0h Disable DLL select.

Set to 1 to disable DLL inside SDRAM.

19-18 reg_sdram_drive R/W 0h SDRAM drive strength.

For DDR1/DDR2, set to 0 for normal, and set to 1 for weak drive

strength.

For DDR3, set to 0 for RZQ/6 and set to 1 for RZQ/7.

For LPDDR1, set to 0 for full, set to 1 for 1/2, set to 2 for 1/4, and set

to 3 for 1/8 drive strength.

All other values are reserved.

17-16 reg_cwl R/W 0h DDR3 CAS Write latency.

Value of 0, 1, 2, and 3 (CAS write latency of 5, 6, 7, and 8) are

supported.

Use the lowest value supported for best performance.

All other values are reserved.

426

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...