GPMC

www.ti.com

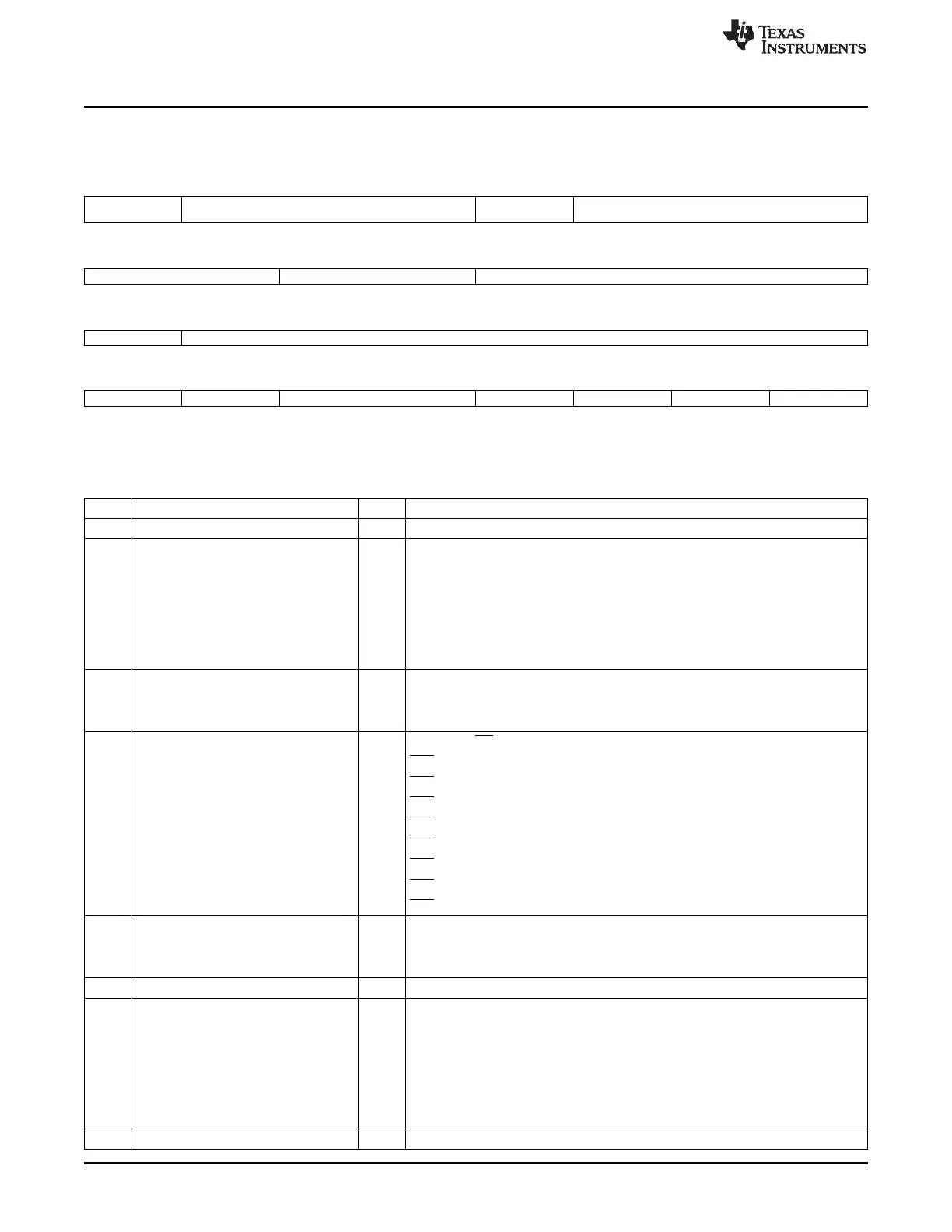

7.1.5.21 GPMC_PREFETCH_CONFIG1

Figure 7-71. GPMC_PREFETCH_CONFIG1

31 30 28 27 26 24

Reserved CYCLEOPTIMIZATION ENABLEOPTIMIZED ENGINECSSELECTOR

ACCESS

R-0 R/W-0 R/W-0 R/W-0

23 22 20 19 16

PFPWENROUNDROBIN Reserved PFPWWEIGHTEDPRIO

R/W-0 R-0 R/W-0

15 14 8

Reserved FIFOTHRESHOLD

R-0 R/W-0

7 6 5 4 3 2 1 0

ENABLEENGINE Reserved WAITPINSELECTOR SYNCHROMODE DMAMODE Reserved ACCESSMODE

R/W-0 R-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0

LEGEND: R = Read only; -n = value after reset

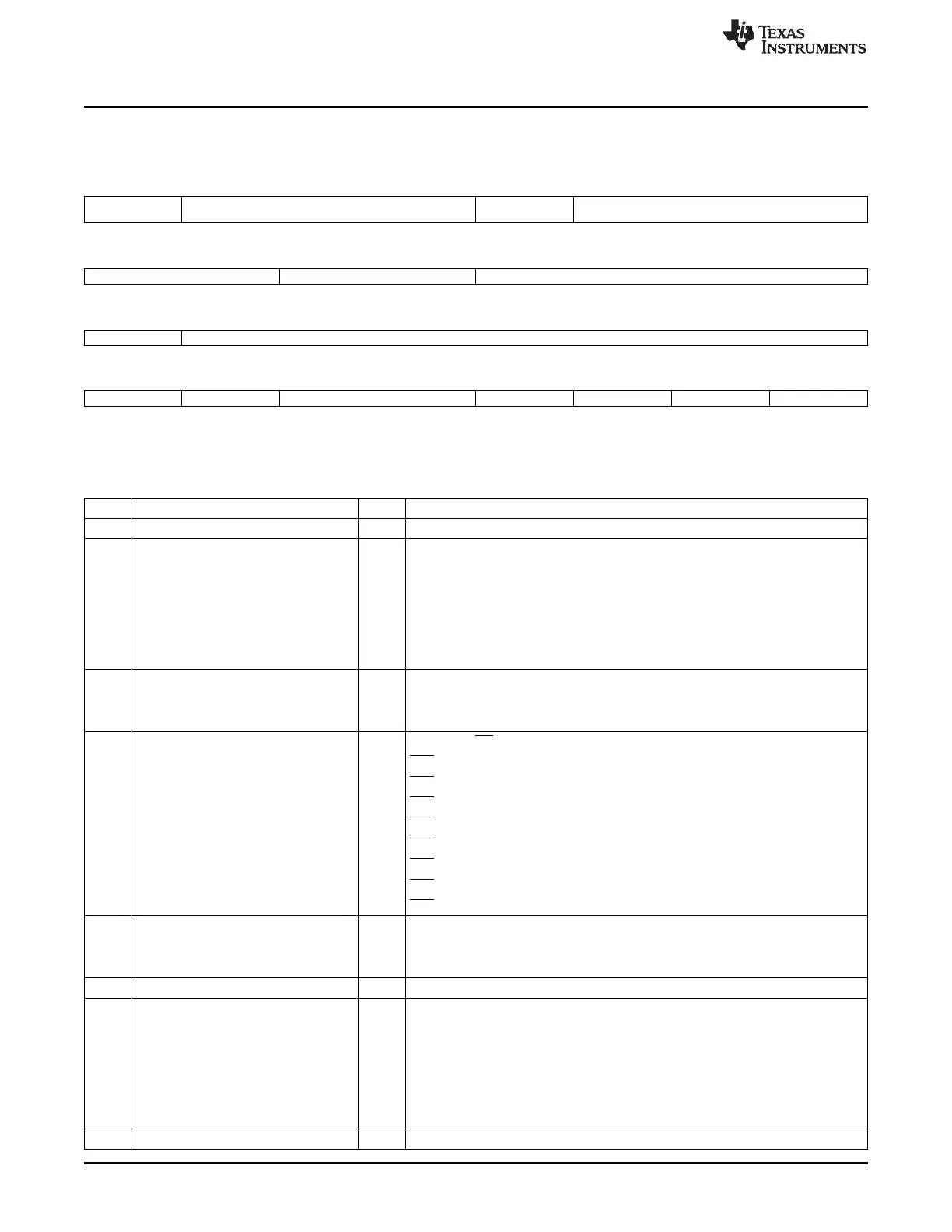

Table 7-75. GPMC_PREFETCH_CONFIG1 Field Descriptions

Bit Field Value Description

31 Reserved 0 Reserved

30-28 CYCLEOPTIMIZATION Define the number of GPMC.FCLK cycles to be substracted from RdCycleTime,

WrCycleTime, AccessTime, CSRdOffTime, CSWrOffTime, ADVRdOffTime,

ADVWrOffTime, OEOffTime, WEOffTime

0 0 GPMC_FCLK cycle

1h 1 GPMC_FCLK cycle

⋮ ⋮

7h 7 GPMC_FCLK cycles

27 ENABLEOPTIMIZEDACCESS Enables access cycle optimization

0 Access cycle optimization is disabled

1 Access cycle optimization is enabled

26-24 ENGINECSSELECTOR Selects the CS where Prefetch Postwrite engine is active

0 CS0

1h CS1

2h CS2

3h CS3

4h CS4

5h CS5

6h CS6

7h CS7

23 PFPWENROUNDROBIN Enables the PFPW RoundRobin arbitration

0 Prefetch Postwrite engine round robin arbitration is disabled

1 Prefetch Postwrite engine round robin arbitration is enabled

22-20 Reserved 0 Reserved

19-16 PFPWWEIGHTEDPRIO When an arbitration occurs between a direct memory access and a PFPW engine

access, the direct memory access is always serviced. If the PFPWEnRoundRobin

is enabled,

0 The next access is granted to the PFPW engine

1h The two next accesses are granted to the PFPW engine

⋮ ⋮

Fh The 16 next accesses are granted to the PFPW engine

15 Reserved 0 Reserved

386

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...