www.ti.com

GPMC

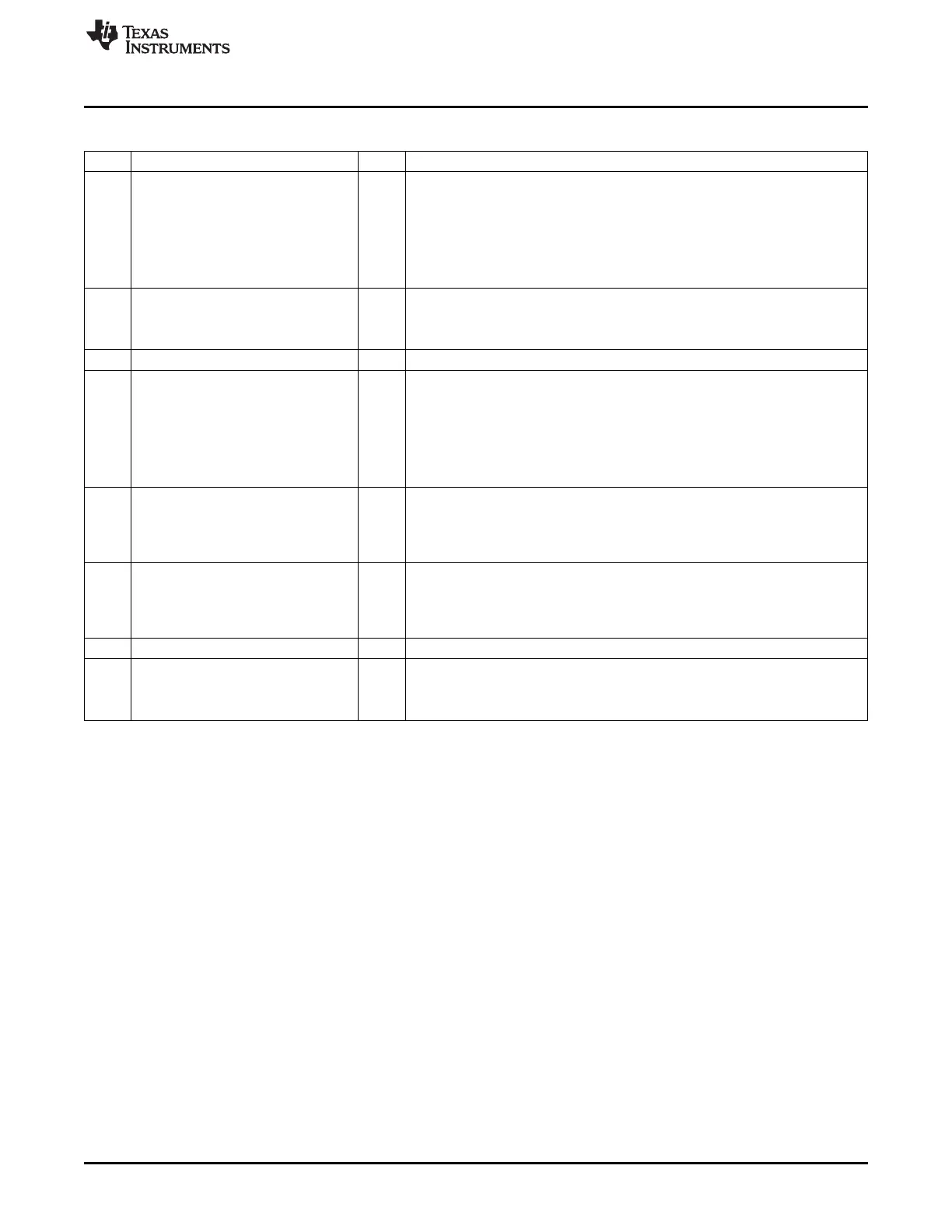

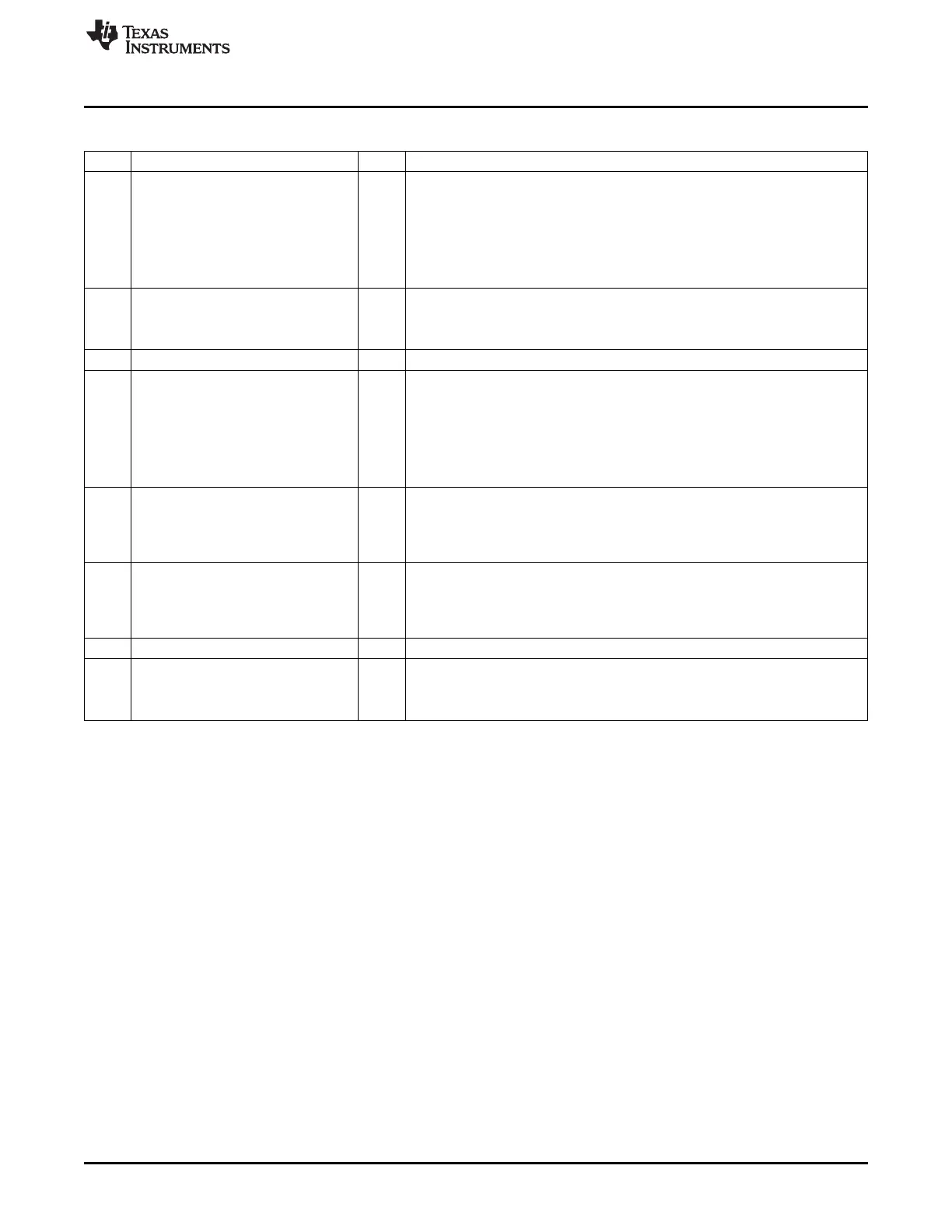

Table 7-75. GPMC_PREFETCH_CONFIG1 Field Descriptions (continued)

Bit Field Value Description

14-8 FIFOTHRESHOLD Selects the maximum number of bytes read from the FIFO or written to the FIFO

by the host on a DMA or interrupt request

0 0 byte

1h 1 byte

⋮ ⋮

40h 64 bytes

7 ENABLEENGINE Enables the Prefetch Postwite engine

0 Prefetch Postwrite engine is disabled

1 Prefetch Postwrite engine is enabled

6 Reserved 0 Reserved

5-4 WAITPINSELECTOR Select which WAIT pin edge detector should start the engine in synchronized

mode

0 Selects Wait0EdgeDetection

1h Selects Wait1EdgeDetection

2h Reserved

3h Reserved

3 SYNCHROMODE Selects when the engine starts the access to CS

0 Engine starts the access to CS as soon as STARTENGINE is set

1 Engine starts the access to CS as soon as STARTENGINE is set AND wait to

non wait edge detection on the selected wait pin

2 DMAMODE Selects interrupt synchronization or DMA request synchronization

0 Interrupt synchronization is enabled. Only interrupt line will be activated on FIFO

threshold crossing.

1 DMA request synchronization is enabled. A DMA request protocol is used.

1 Reserved 0 Reserved

0 ACCESSMODE Selects pre-fetch read or write posting accesses

0 Prefetch read mode

1 Write-posting mode

387

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...