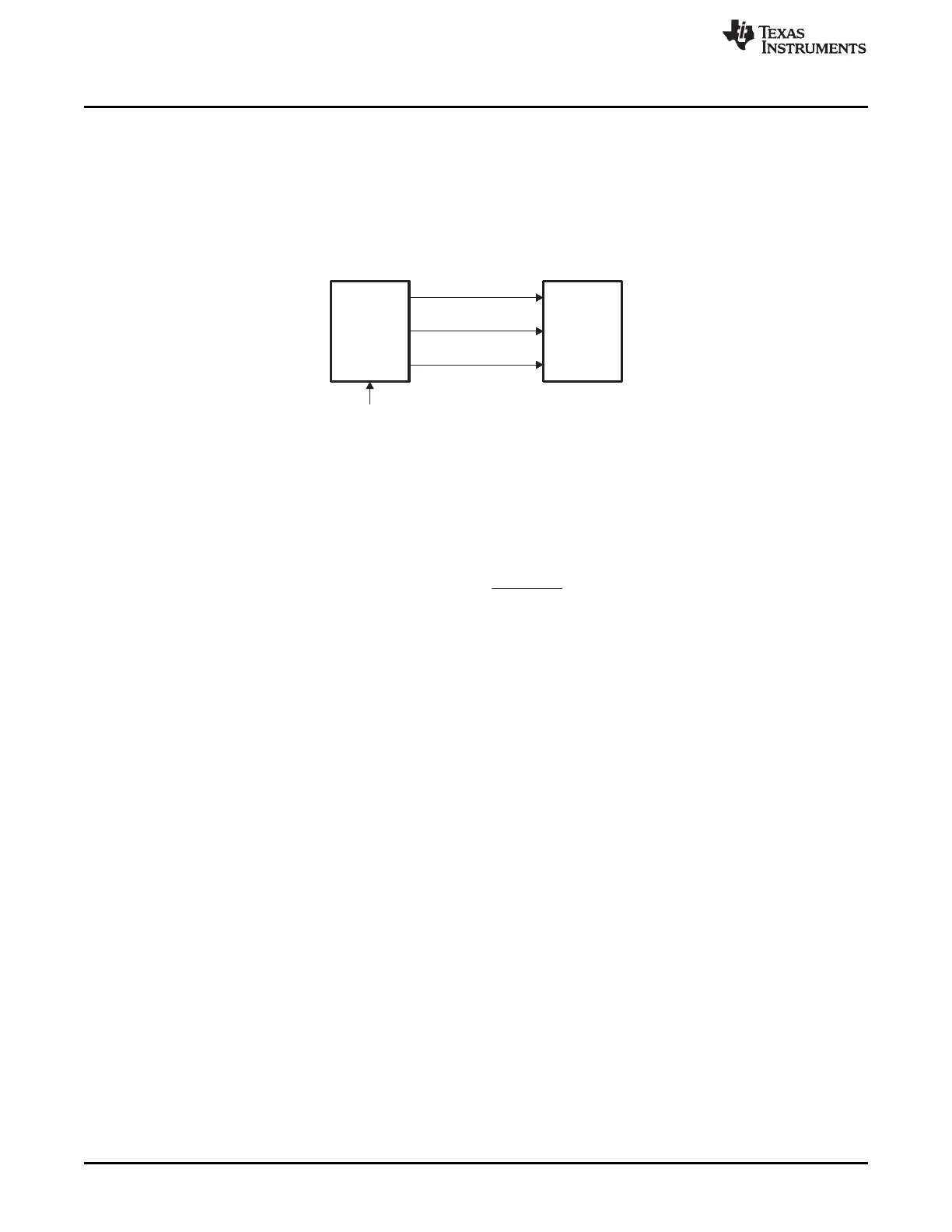

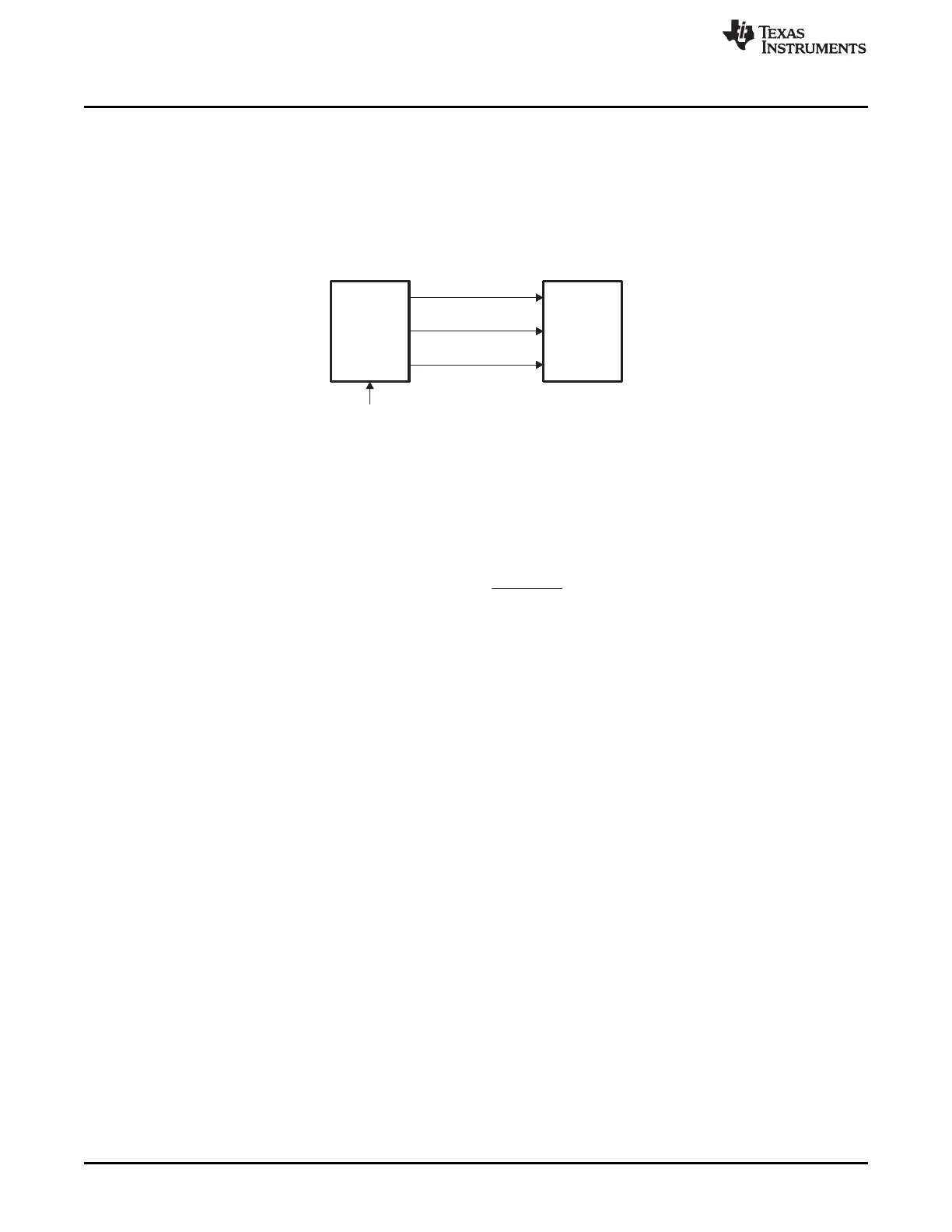

PixelClockDerived

fromLCD_CLK

HSYNC/LineClock

VSYNC/FrameClock

LCD

Controller

Display

LCD_CLK

Functional Description

www.ti.com

13.3 Functional Description

13.3.1 Clocking

This section details the various clocks and signals. Figure 13-3 shows input and output LCD controller

clocks.

Figure 13-3. Input and Output Clocks

13.3.1.1 Pixel Clock (LCD_PCLK)

The pixel clock (LCD_PCLK) frequency is derived from LCD_CLK, the reference clock to this LCD module

(see Figure 13-3). The pixel clock is used by the LCD display to clock the pixel data into the line shift

register.

where CLKDIV is a field in the LCD_CTRL register and should not be 0 or 1.

• Passive (STN) mode. LCD_PCLK only transitions when valid data is available for output. It does not

transition when the horizontal clock (HSYNC) is asserted or during wait state insertion.

• Active (TFT) mode. LCD_PCLK continuously toggles as long as the Raster Controller is enabled.

1102

LCD Controller SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...