www.ti.com

CONTROL_MODULE Registers

9.3.78 sma2 Register (offset = 1320h) [reset = 0h]

The VSLDO_CORE_AUTO_RAMP_EN bit when set, allows the VSLDO to be put into retention during

deep-sleep thereby enabling lower power consumption. Since the VSLDO is shared b/w WKUP M3

memories and CORE memories, the VSLDO has to be brought out of retention on any wakeup event. The

hardware scheme mentioned below achieves this purpose.

sma2 is shown in Figure 9-81 and described in Table 9-88.

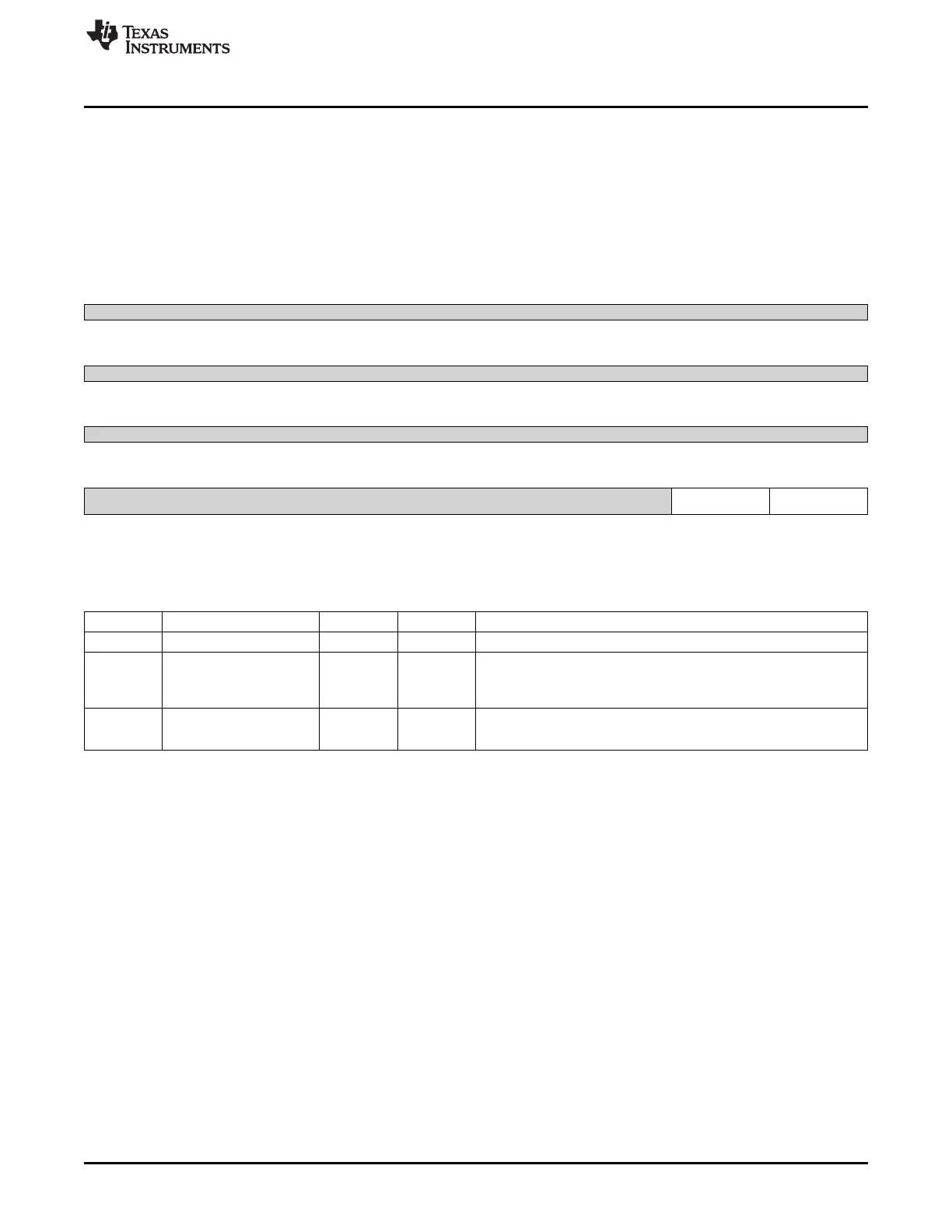

Figure 9-81. sma2 Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved vsldo_core_auto_ram rmii2_crs_dv_mode_s

p_en el

R-0h R/W0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

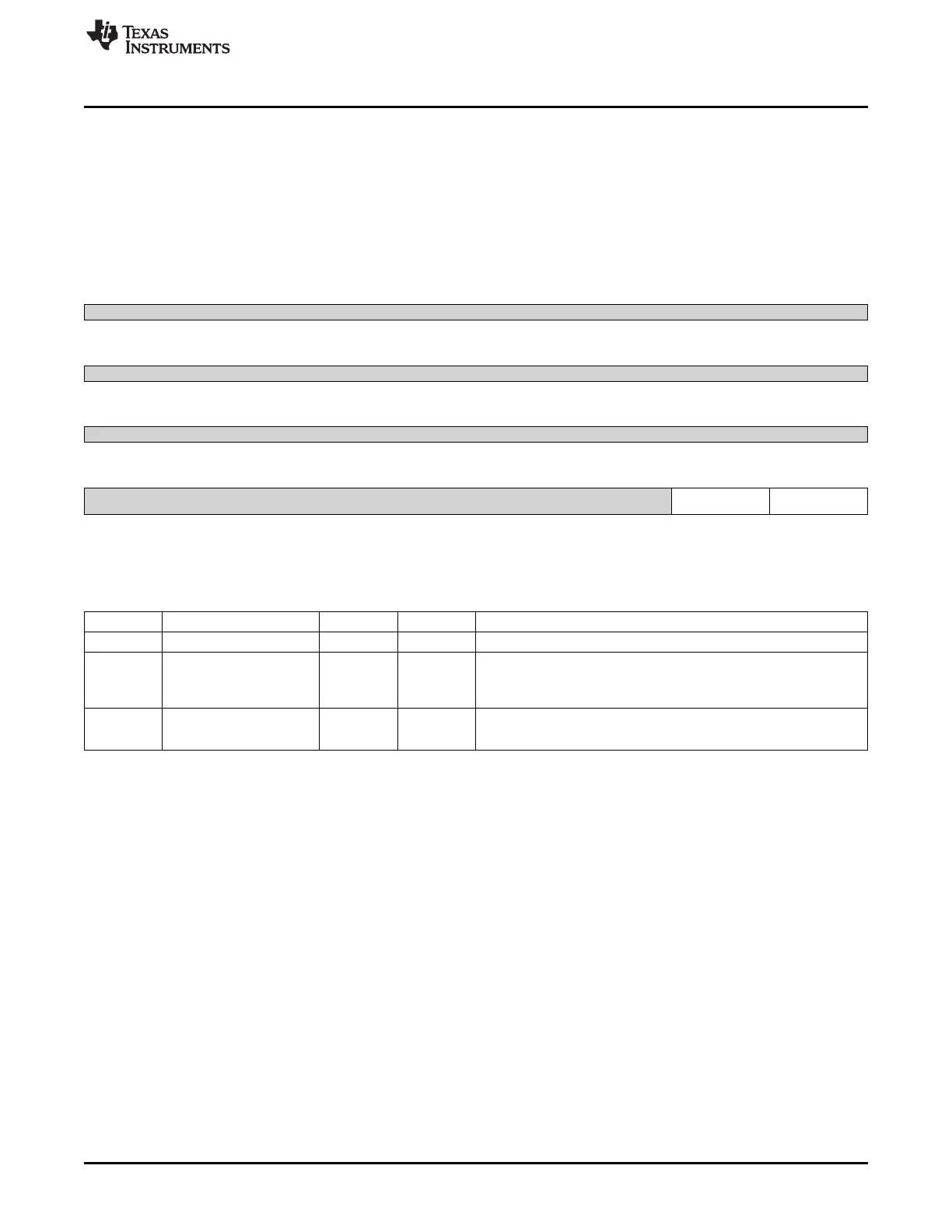

Table 9-88. sma2 Register Field Descriptions

Bit Field Type Reset Description

31-2 Reserved R 0h

1 vsldo_core_auto_ramp_en R/W 0h

0: PRCM controls VSLDO.

1: Allows hardware to bring VSLDO out of retention on wakeup from

deep-sleep.

0 rmii2_crs_dv_mode_sel R/W 0h

0: Select MMC2_DAT7 on GPMC_A9 pin in MODE3.

1: Select RMII2_CRS_DV on GPMC_A9 pin in MODE3.

843

SPRUH73H–October 2011–Revised April 2013 Control Module

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...