Host 32 Bits (16 Bits Addressable)

OCP Interface

TCLR TTGR TLDR TCRR TMAR

TSICR TWPS

TIO CP_CFG

TISTAT

porgpocfg

pieventcapt

Edge Detection

Logic

piclktimer

Prescaler

Timer

Counter

COMP

Pulse

Pwm

Logic

IRQENABLE_SET

pointr_req

pointr_pend

pointr_swakeup

pifclken

pid1ereq

piocpmconnect

porocpsconnect

portimerpwm

poidleack

TCAR

1/2

IRQENABLE_CLR

IRQSTATUS

IRQWAKEEN

IRQSTATUS_RAW

DMTimer

www.ti.com

Table 20-1. Timer Resolution and Maximum Range

Clock Prescaler Resolution Interrupt Period Range

32.768 KHz 1 (min) 31.25 us 31.25 us to ~36h 35m

256 (max) 8 ms 8 ms to ~391d 22h 48m

25 MHz 1 (min) 40 ns 40 ns to ~171.8s

256 (max) 10.24 us ~20.5 us to ~24h 32m

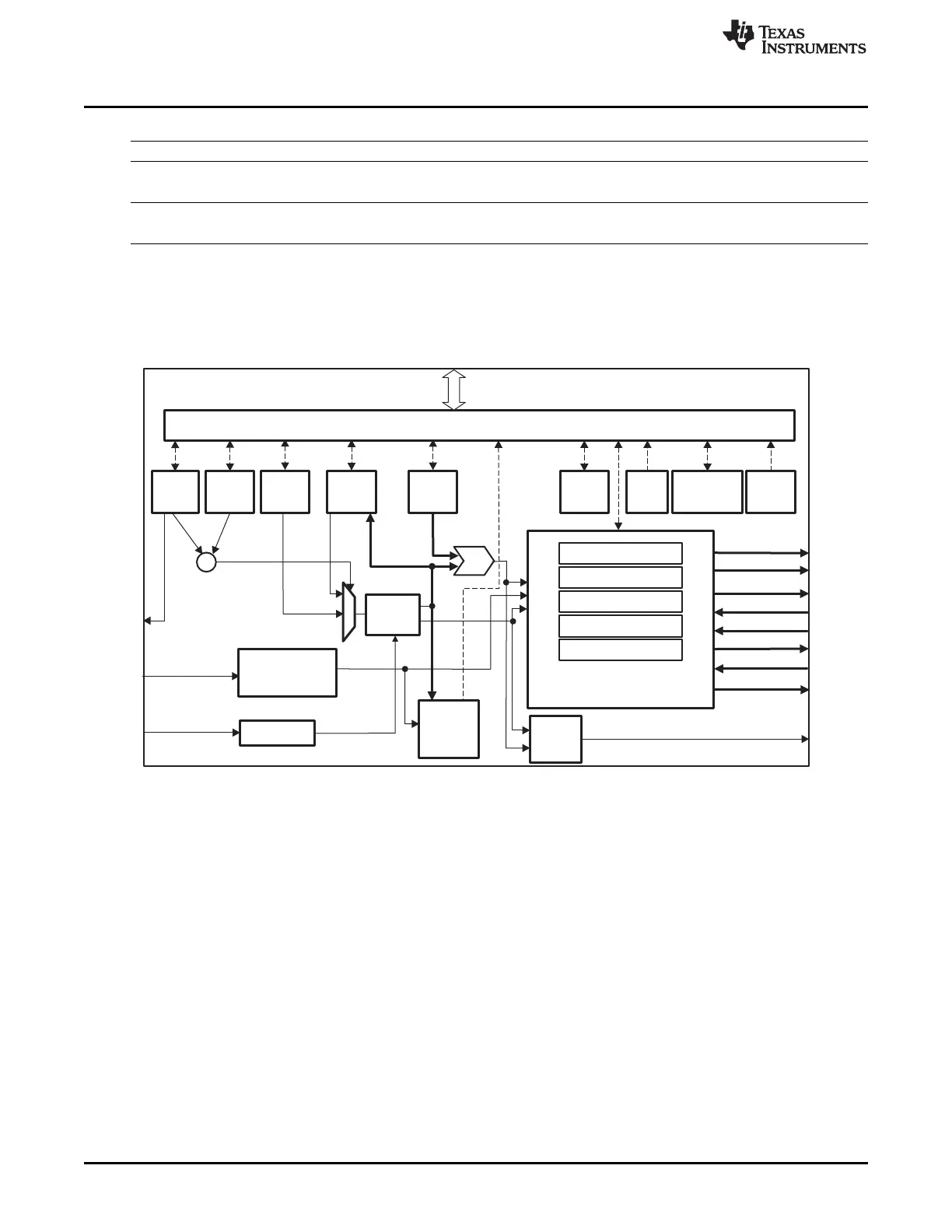

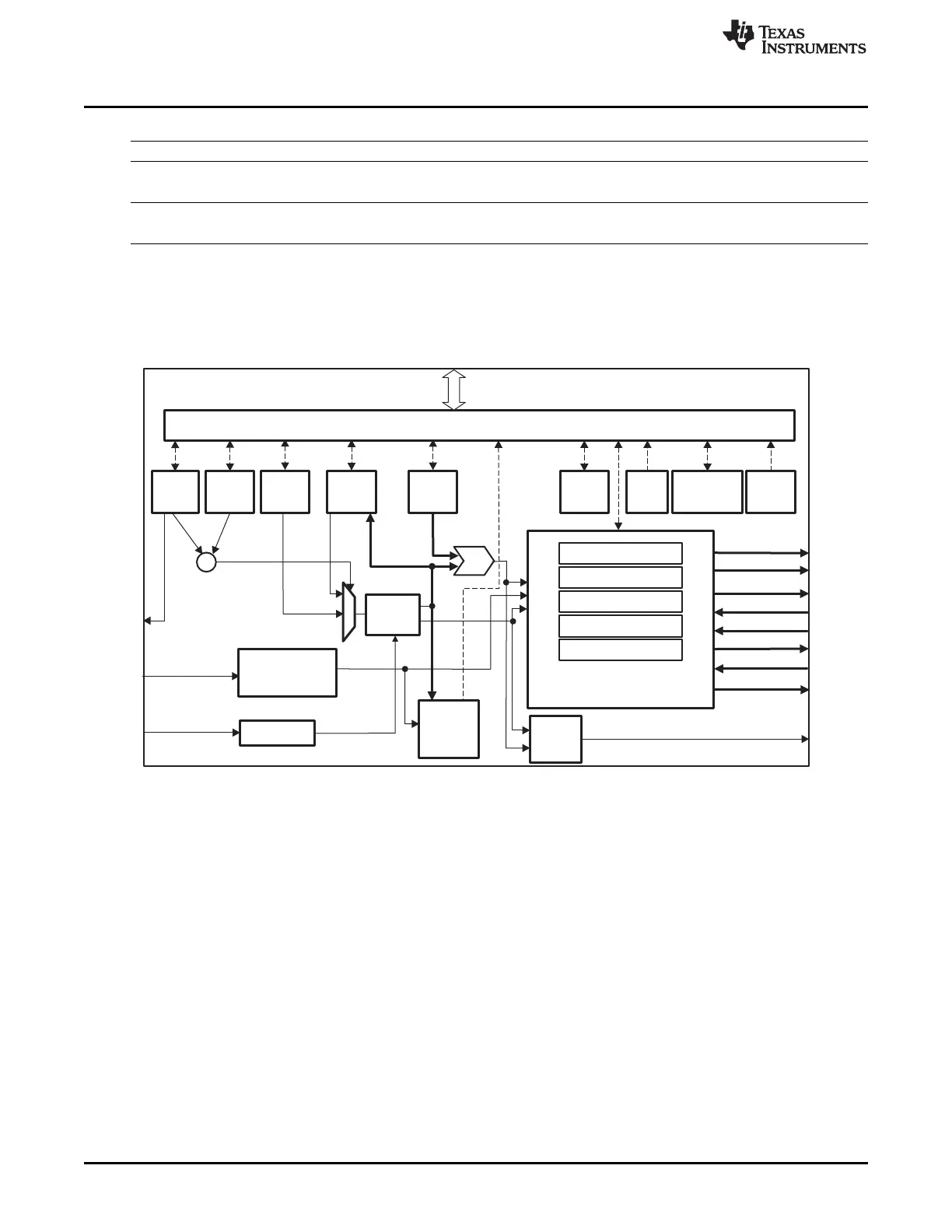

20.1.1.3 Functional Block Diagram

Figure 20-1 shows a block diagram of the timer.

Figure 20-1. Timer Block Diagram

3552

Timers SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...