DMTimer 1ms

www.ti.com

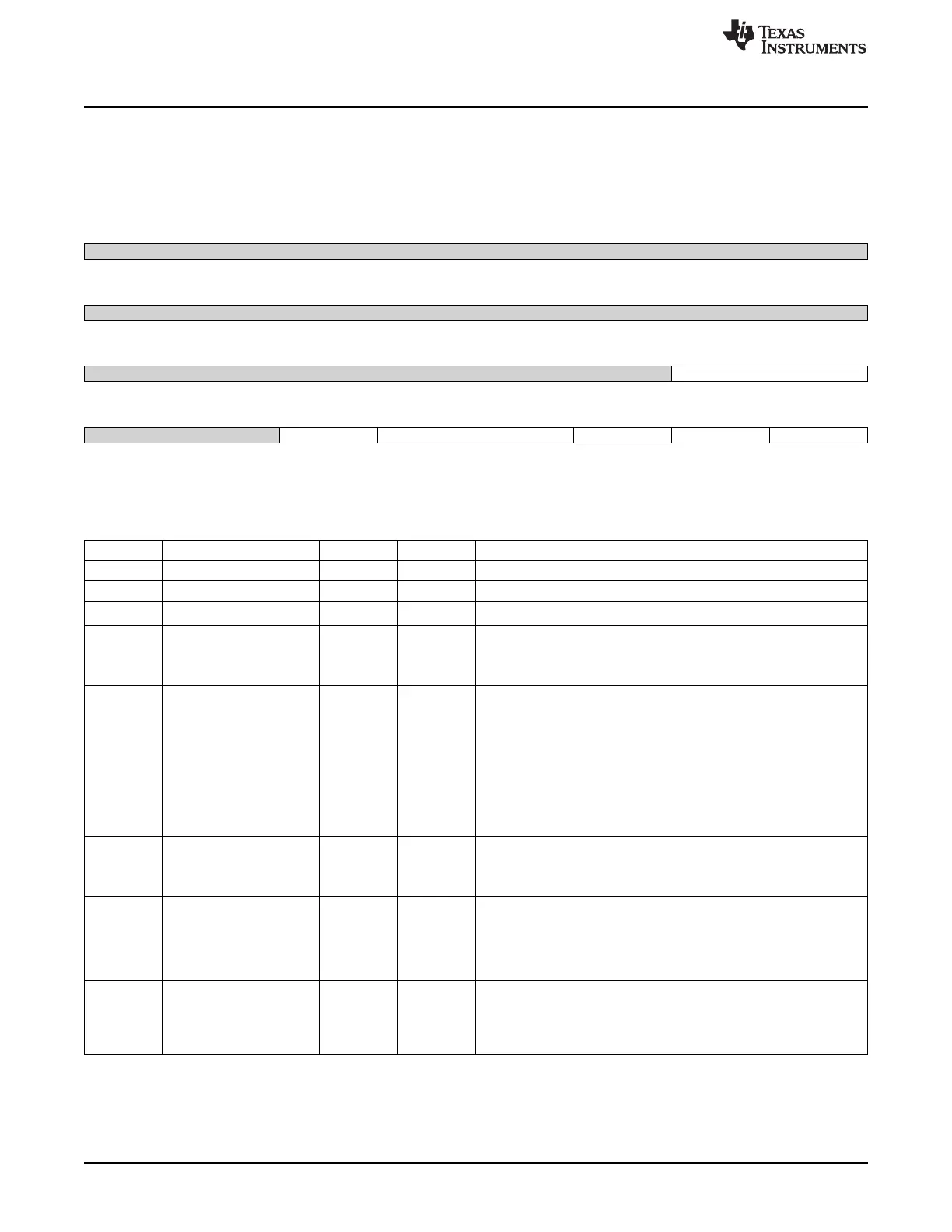

20.2.5.2 TIOCP_CFG Register (offset = 10h) [reset = 0h]

TIOCP_CFG is shown in Figure 20-36 and described in Table 20-37.

This register controls the various parameters of the OCP interface

Figure 20-36. TIOCP_CFG Register

31 30 29 28 27 26 25 24

Reserved

R/W-0h

23 22 21 20 19 18 17 16

Reserved

R/W-0h

15 14 13 12 11 10 9 8

Reserved ClockActivity

R/W-0h R/W-0h

7 6 5 4 3 2 1 0

Reserved EmuFree IdleMode EnaWakeup SoftReset AutoIdle

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

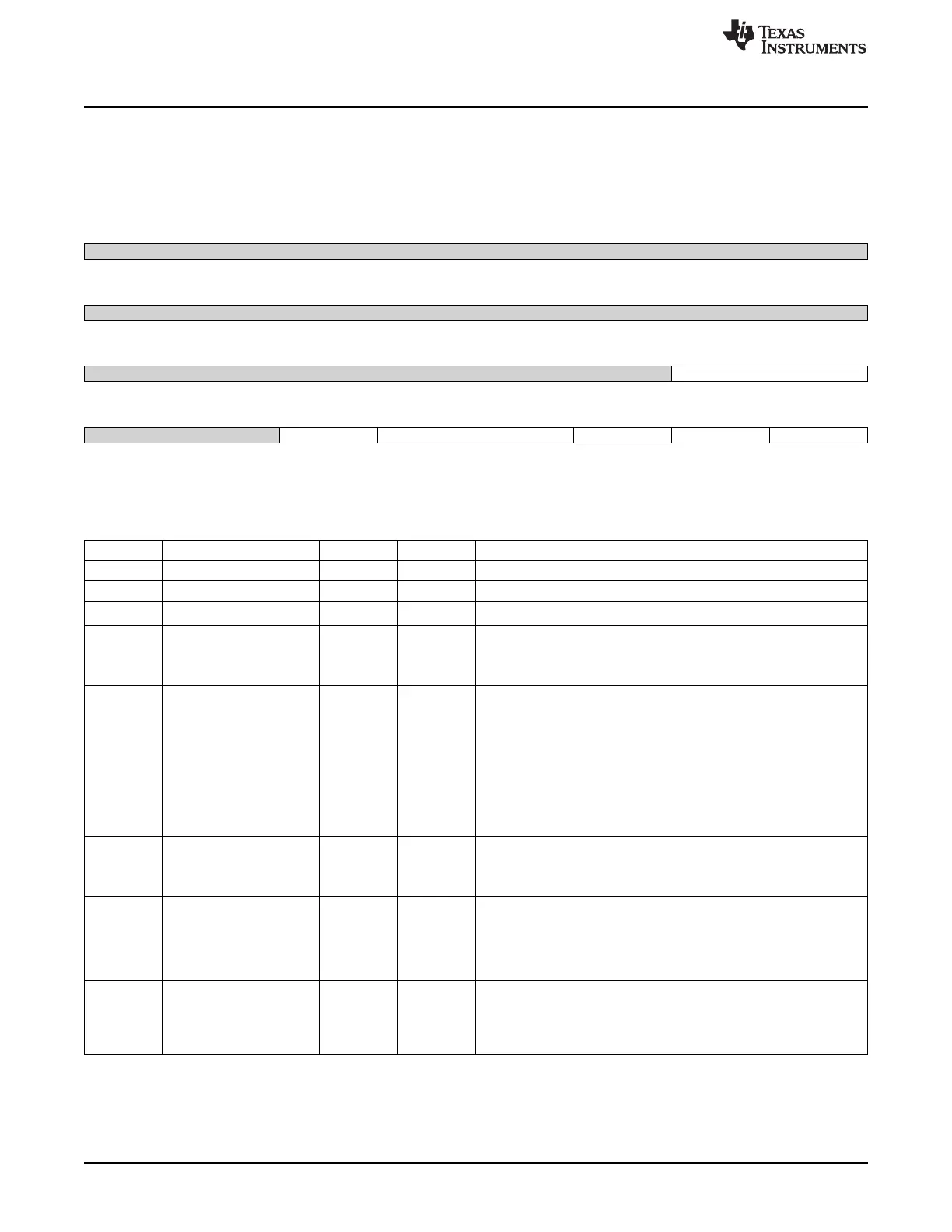

Table 20-37. TIOCP_CFG Register Field Descriptions

Bit Field Type Reset Description

31-10 Reserved R/W 0h

9-8 ClockActivity R/W 0h

7-6 Reserved R/W 0h

Write 0's for future compatibility Reads return 0

5 EmuFree R/W 0h

Emulation mode

0 = timer_frozen : Timer counter frozen in emulation

1 = timer_free : Timer counter free-running in emulation

4-3 IdleMode R/W 0h

Power Management, req/ack control

0 = fidle : Force-idle. An idle request is acknowledged

unconditionally

1 = nidle : No-idle. An idle request is never acknowledged

2 = sidle : Smart-idle. Acknowledgment to an idle request is given

based on the internal activity of the module

3 = Smart-idle wakeup capable. Acknowledgment to an idle request

is given based on the internal activity of the module. The module

may generate wakeup events when in idle state.

2 EnaWakeup R/W 0h

Wake-up feature global control

0 = nowake : No wakeup line assertion in idle mode

1 = enbwake : Wakeup line assertion enabled in smart-idle mode

1 SoftReset R/W 0h Software reset.

This bit is automatically reset by the hardware.

During reads, it always return 0

0 = nmode : Normal mode

1 = rstmode : The module is reset

0 AutoIdle R/W 0h

Internal OCP clock gating strategy

0 = clkfree : OCP clock is free-running

1 = clkgate : Automatic OCP clock gating strategy is applied, based

on the OCP interface activity

3600

Timers SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...