USB Registers

www.ti.com

16.5.7.2 QMGRRST Register (offset = 8h) [reset = 0h]

QMGRRST is shown in Figure 16-278 and described in Table 16-292.

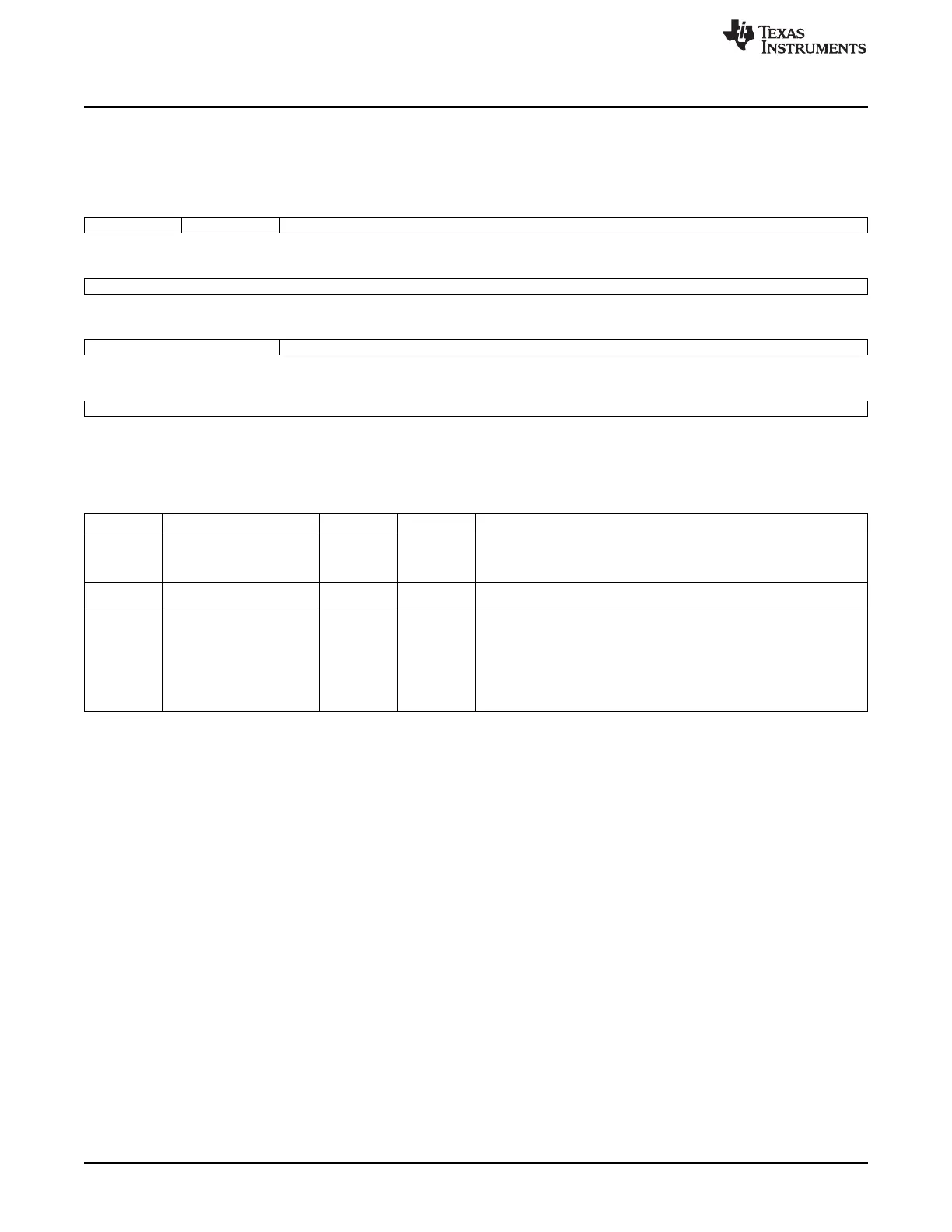

Figure 16-278. QMGRRST Register

31 30 29 28 27 26 25 24

HEAD_TAIL Reserved DEST_QNUM

W-0 W-0

23 22 21 20 19 18 17 16

DEST_QNUM

W-0

15 14 13 12 11 10 9 8

Reserved SOURCE_QNUM

W-0

7 6 5 4 3 2 1 0

SOURCE_QNUM

W-0

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

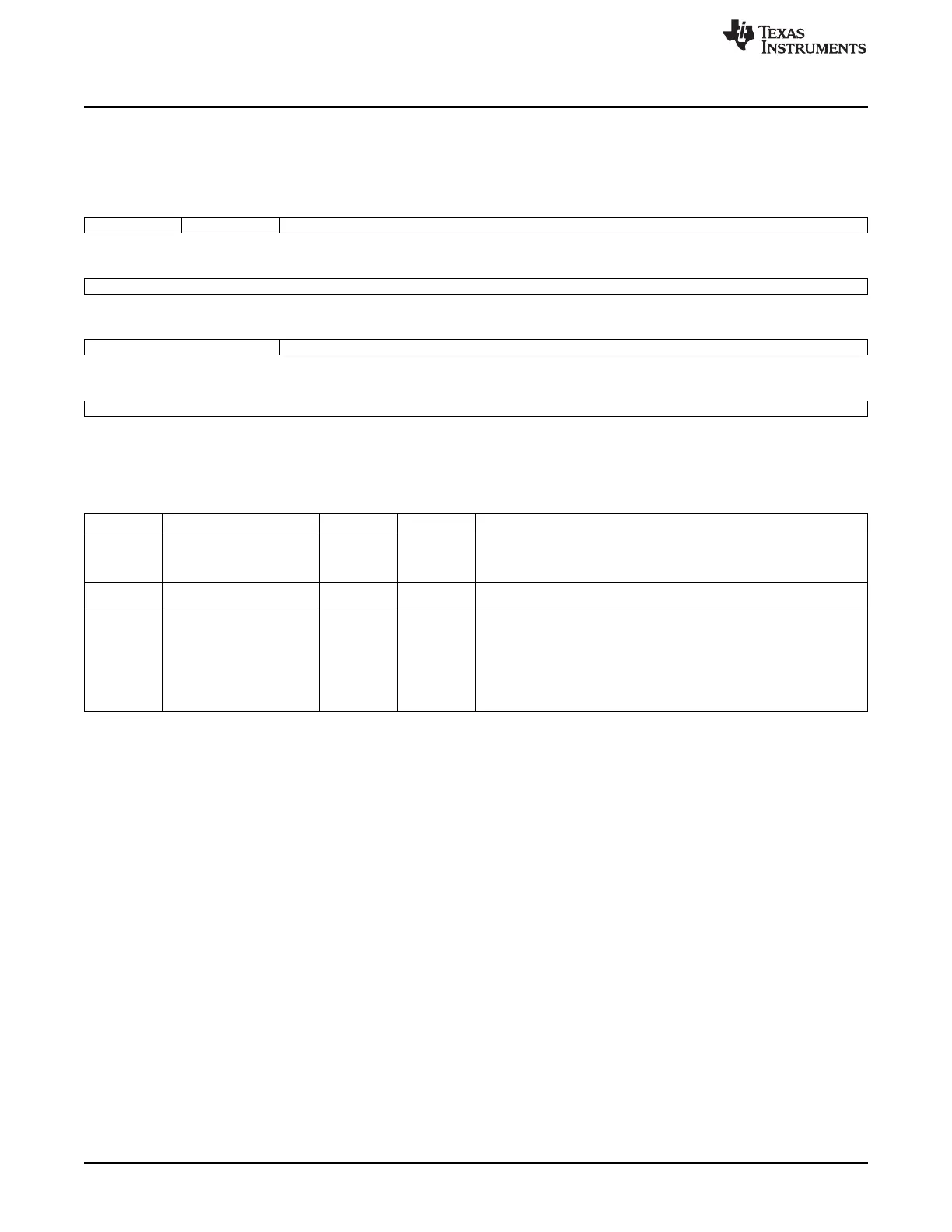

Table 16-292. QMGRRST Register Field Descriptions

Bit Field Type Reset Description

31 HEAD_TAIL W-0 0 Indicates whether queue contents should be merged on to head or

tail of destination queue.

Clear this field for head and set for tail.

29-16 DEST_QNUM W-0 0

Destination Queue Number

13-0 SOURCE_QNUM W-0 0 Source Queue Number Queue Manager Queue Diversion Register

Note : CBA write transactions to this register cause the QMGR to

start processing an internal state machine.

This disables CBA read transactions.while it is busy processing the

state machine.

Once the state machine is back in the idle state

CBA read transactions are available again.

2110

Universal Serial Bus (USB) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...