www.ti.com

EDMA3 Registers

11.4.1.2.3 QDMA Event Missed Register (QEMR)

For a particular QDMA channel, if two QDMA events are detected without the first event getting

cleared/serviced, the bit corresponding to that channel is set/asserted in the QDMA event missed register

(QEMR). The QEMR bits for a channel are also set if a QDMA event on the channel encounters a NULL

entry (or a NULL TR is serviced). If any QEMR bit is set (and all errors, including bits in other error

registers (EMR/EMRH, CCERR) were previously cleared), the EDMA3CC generates an error interrupt. For

details on EDMA3CC error interrupt generation, see Error Interrupts.

The QEMR is shown in Figure 11-54 and described in Table 11-39.

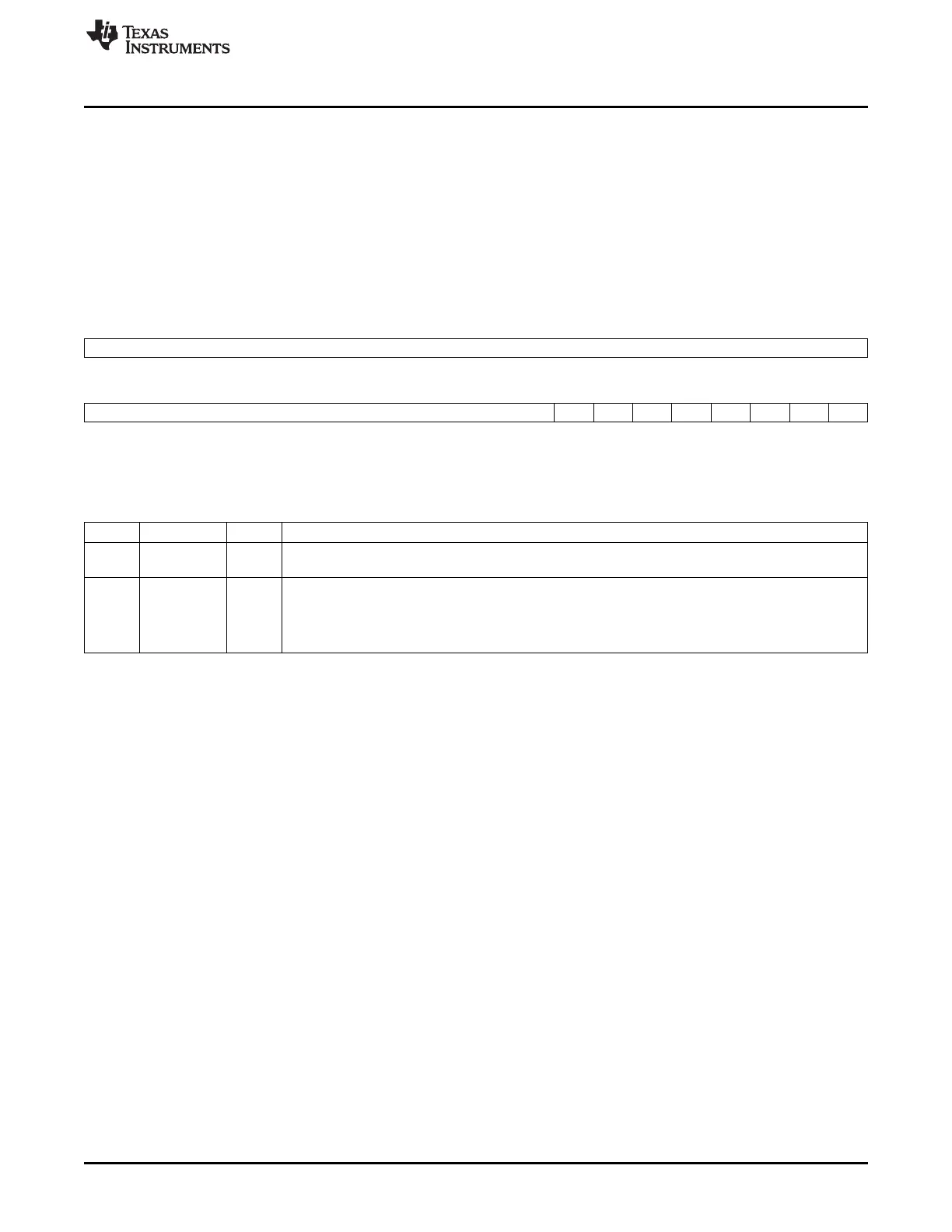

Figure 11-54. QDMA Event Missed Register (QEMR)

31 16

Reserved

R-0

15 7 6 5 4 3 2 1 0

Reserved E7 E6 E5 E4 E3 E2 E1 E0

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

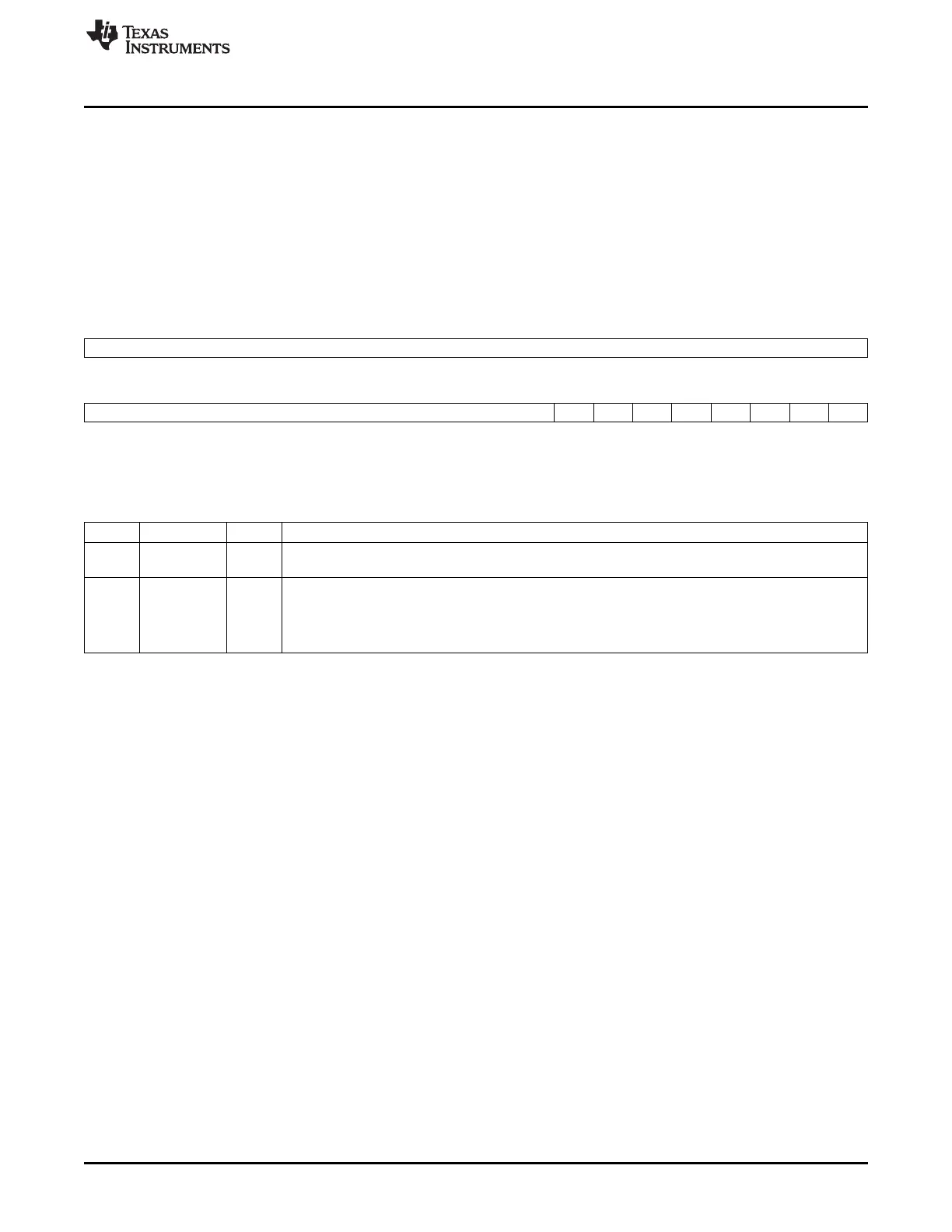

Table 11-39. QDMA Event Missed Register (QEMR) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

7-0 En Channel 0-7 QDMA event missed. En is cleared by writing a 1 to the corresponding bit in the QDMA

event missed clear register (QEMCR).

0 No missed event.

1 Missed event occurred.

953

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...