www.ti.com

Functional Description

26.1.10.2 Execution

The image is executed at the time the ROM Code performs the branch to the first executable instruction

inside the Initial SW. For a GP Device in non-XIP, the execution address is the first word after the GP

header. The branch is performed in public ARM supervisor mode. The R0 register points to the Booting

Parameters structure which contains various information about the booting execution. Table 26-40 details

this structure.

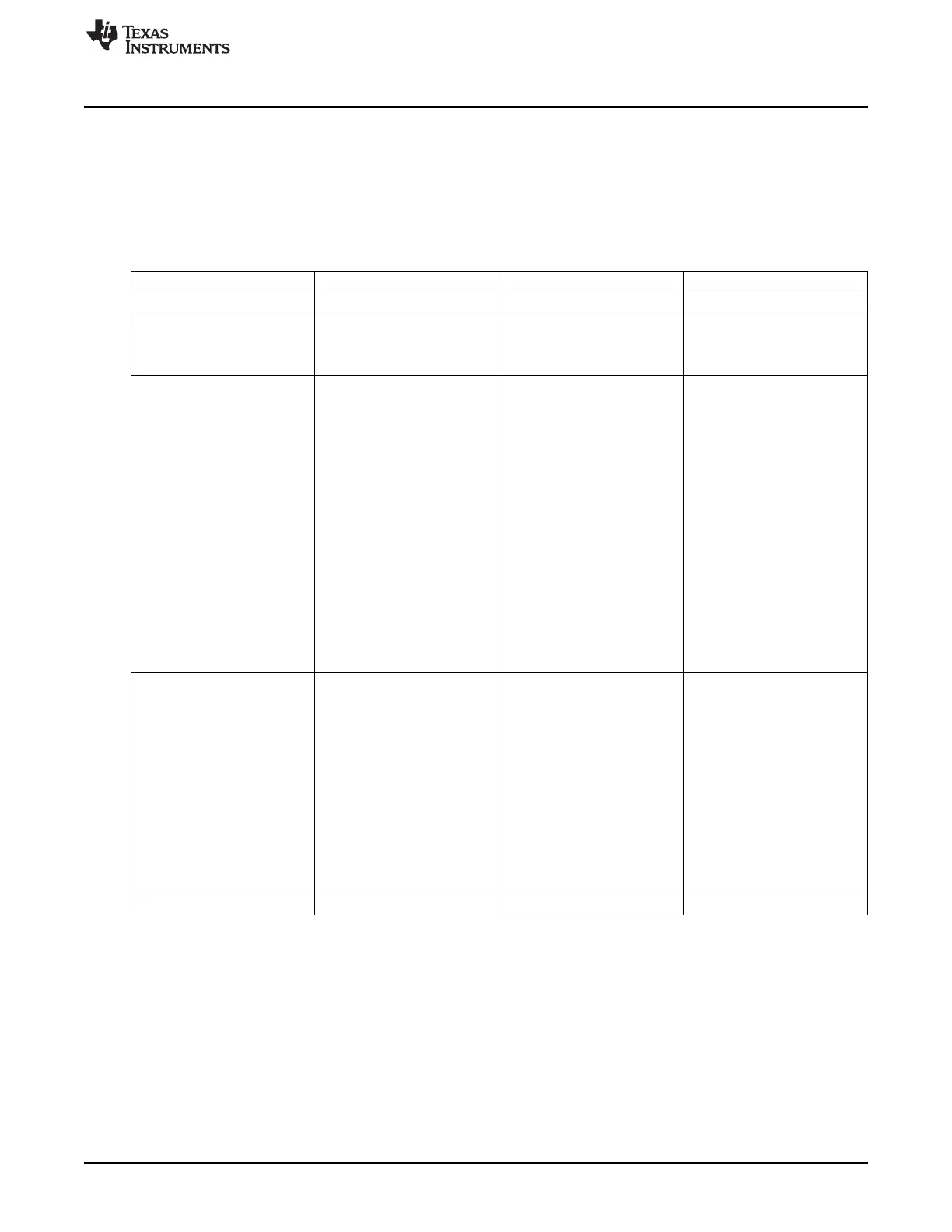

Table 26-40. Booting Parameters Structure

Offset Field Size[bytes] Description

00h Reserved 4 Reserved

Pointer to the memory device

Memory booting device descriptor that has been used

04h 4

descriptor address during the memory booting

process.

(1)

Code of device used for

booting

00h – void, no device

01h – XIP MUX1 memory

02h – XIPWAIT MUX 1 (wait

monitoring on)

03h – XIP MUX2 memory

04h – XIPWAIT MUX 2 (wait

monitoring on)

08h Current Booting Device 1

05h – NAND

06h – NAND with I2C

08h – MMC/SD port 0

09h – MMC/SD port 1

15h – SPI

41h – UART0

44h – USB

46h – CPGMAC0

Current reset reason bit mask

(bit=1-event present)

[0] – Power-on (cold) reset

[1] – Global warm software

reset

[2] – Reserved

09h Reset Reason 1

[3] – Reserved

[4] – WDT1 timer reset

[5] – Global external warm

reset

Other bits – Reserved

Note: ROM code does not

clear any of these bits.

0Ah Reserved 1 Reserved

(1)

More detailed information is found in each memory's booting description.

4151

SPRUH73H–October 2011–Revised April 2013 Initialization

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...