www.ti.com

GPIO Registers

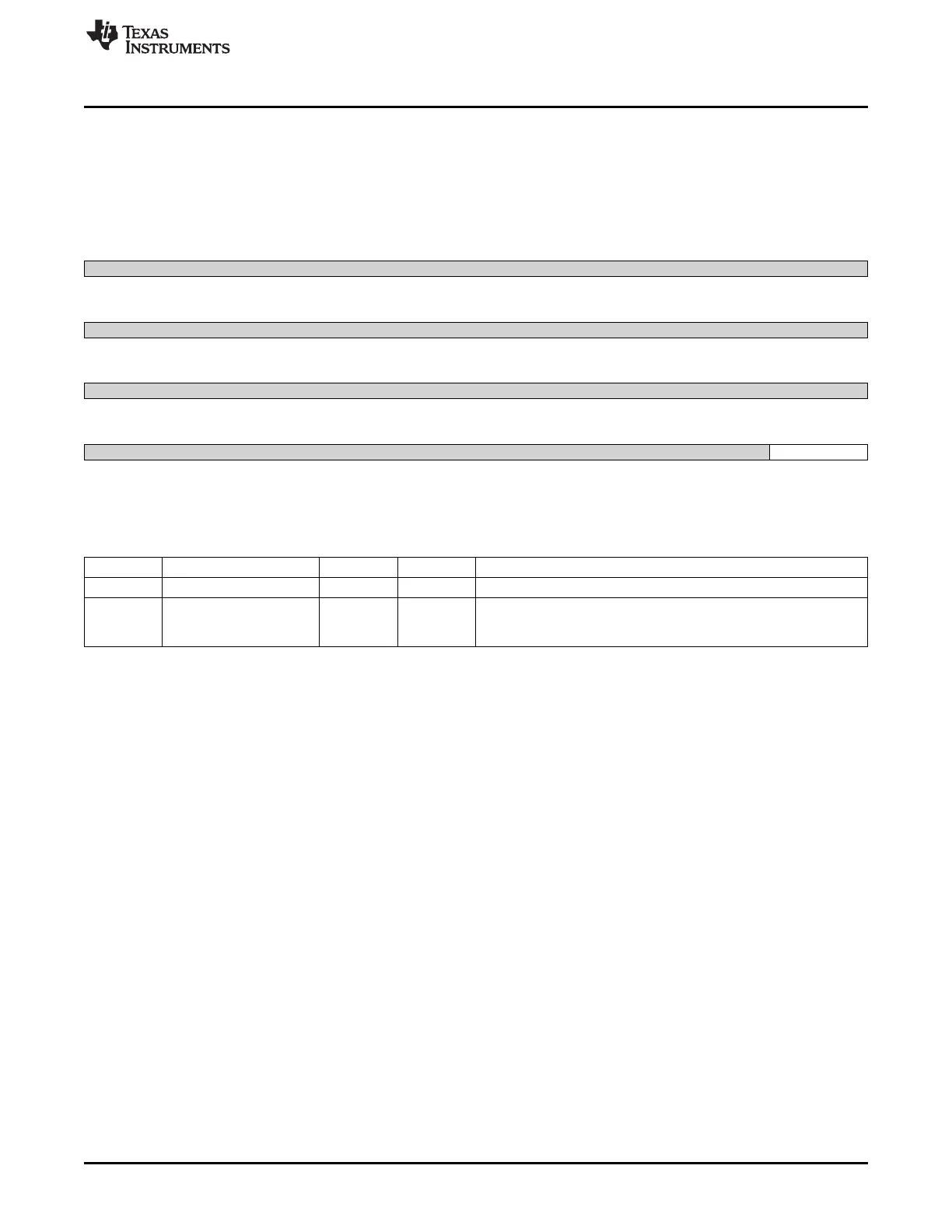

25.4.1.3 GPIO_EOI Register (offset = 20h) [reset = 0h]

GPIO_EOI is shown in Figure 25-9 and described in Table 25-8.

This module supports DMA events with its interrupt signal. This register must be written to after the DMA

completes in order for subsequent DMA events to be triggered from this module.

Figure 25-9. GPIO_EOI Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved DMAEvent_Ack

R-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

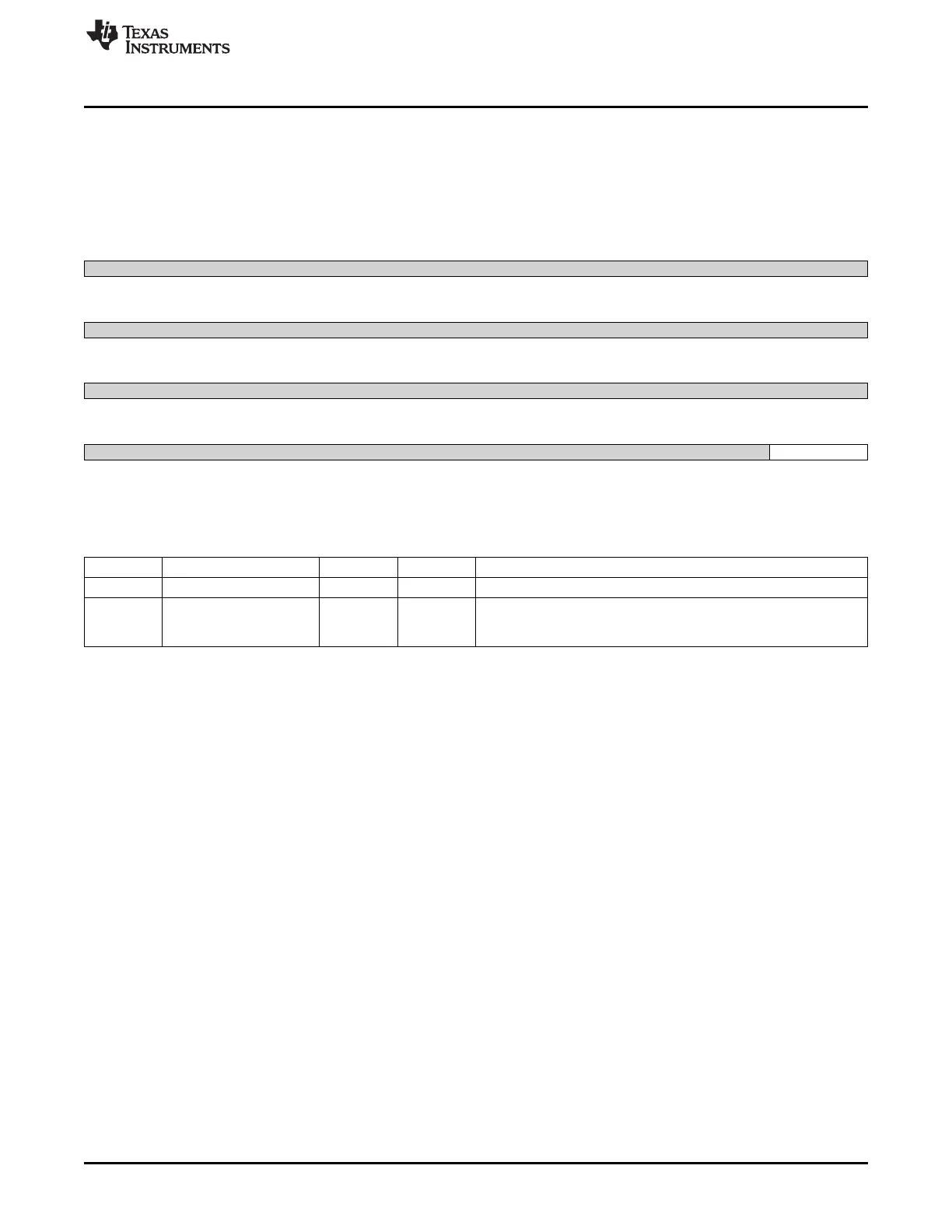

Table 25-8. GPIO_EOI Register Field Descriptions

Bit Field Type Reset Description

31-1 Reserved R 0h

0 DMAEvent_Ack R/W 0h Write 0 to acknowledge DMA event has been completed. Module will

be able to generate another DMA event only when the previous one

has been acknowledged using this register. Reads always returns 0.

4071

SPRUH73H–October 2011–Revised April 2013 General-Purpose Input/Output

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...