www.ti.com

Ethernet Subsystem Registers

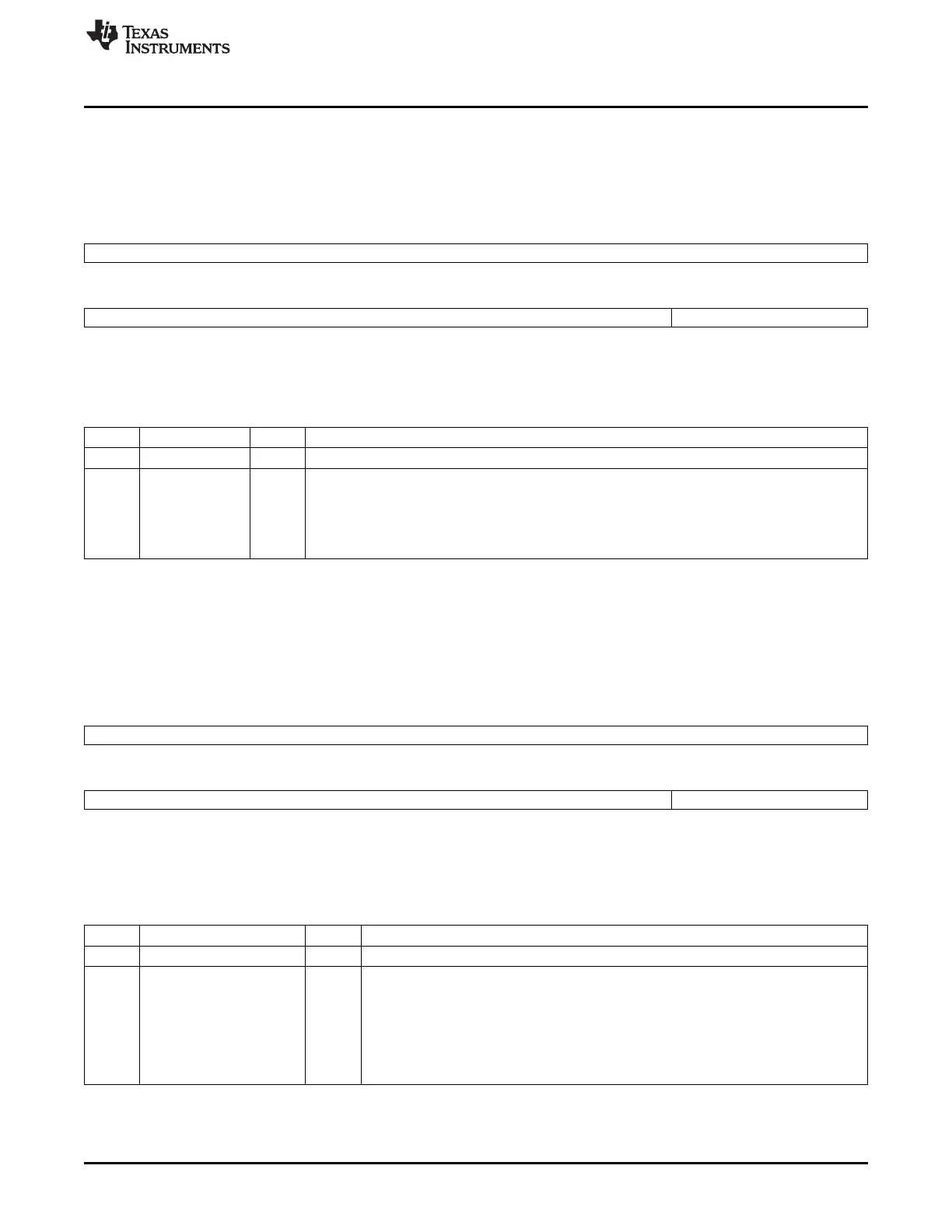

14.5.10.5 MDIO Link Status Change Interrupt Register (MDIOLINKINTRAW)

The MDIO link status change interrupt register (MDIOLINKINTRAW) is shown in Figure 14-236 and

described in Table 14-255.

Figure 14-236. MDIO Link Status Change Interrupt Register (MDIOLINKINTRAW)

31 16

Reserved

R-0x0

15 2 1 0

Reserved LINKINTRAW

R-0x0 RWC-0x0

LEGEND: RWC = Read/Write/Clear; R = Read only; -n = value after reset

Table 14-255. MDIO Link Status Change Interrupt Register (MDIOLINKINTRAW) Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reserved.

1-0 LINKINTRAW 0-3h MDIO link change event, raw value. When asserted 1, a bit indicates that there was an MDIO link

change event (i.e. change in the MDIOLINK register) corresponding to the PHY address in the

MDIOUSERPHYSELn register. LINKINTRAW[0] and LINKINTRAW[1] correspond to

MDIOUSERPHYSEL0 and MDIOUSERPHYSEL1, respectively. Writing a 1 will clear the event and

writing 0 has no effect. If the INTTESTENB bit in the MDIOCONTROL register is set, the host may

set the LINKINTRAW bits to a 1. This mode may be used for test purposes.

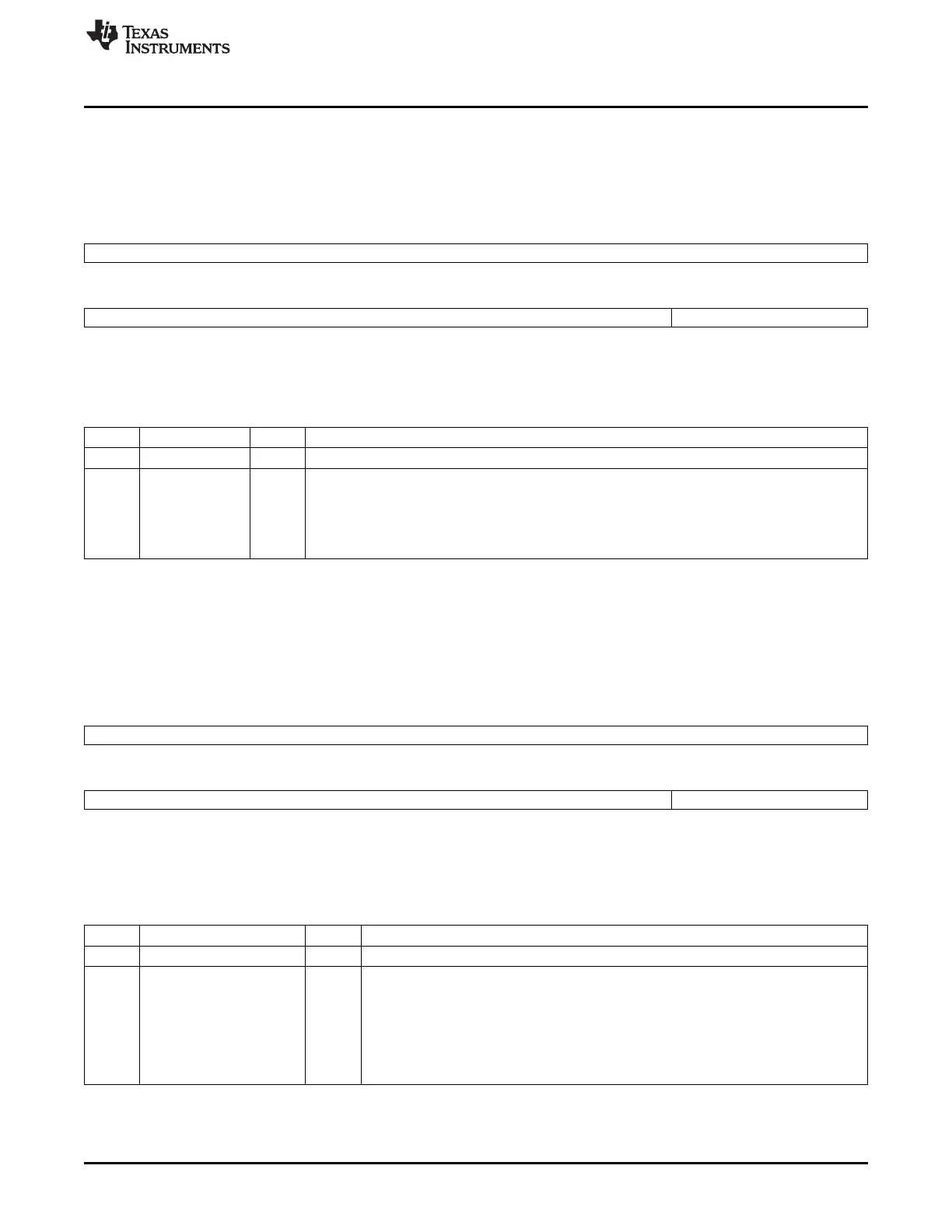

14.5.10.6 MDIO Link Status Change Interrupt Register (Masked Value) (MDIOLINKINTMASKED)

The MDIO link status change interrupt register (Masked Value) (MDIOLINKINTMASKED) is shown in

Figure 14-237 and described in Table 14-256.

Figure 14-237. MDIO Link Status Change Interrupt Register (Masked Value)

(MDIOLINKINTMASKED)

31 16

Reserved

R-0x0

15 2 1 0

Reserved LINKINTMASKED

R-0x0 RWC-0x0

LEGEND: RWC = Read/Write/Clear; R = Read only; -n = value after reset

Table 14-256. MDIO Link Status Change Interrupt Register (Masked Value) (MDIOLINKINTMASKED)

Field Descriptions

Bit Field Value Description

31-2 Reserved 0 Reserved.

1-0 LINKINTMASKED 0-3h MDIO link change interrupt, masked value. When asserted 1, a bit indicates that there

was an MDIO link change event (i.e. change in the MDIO Link register) corresponding to

the PHY address in the MDIOUSERPHYSELn register and the corresponding

LINKINTENB bit was set. LINKINTMASKED[0] and LINKINTMASKED[1] correspond to

MDIOUSERPHYSEL0 and MDIOUSERPHYSEL1, respectively. Writing a 1 will clear the

interrupt and writing 0 has no effect. If the INTTESTENB bit in the MDIOCONTROL

register is set, the host may set the LINKINT bits to a 1. This mode may be used for test

purposes.

1477

SPRUH73H–October 2011–Revised April 2013 Ethernet Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...