www.ti.com

DMTimer 1ms

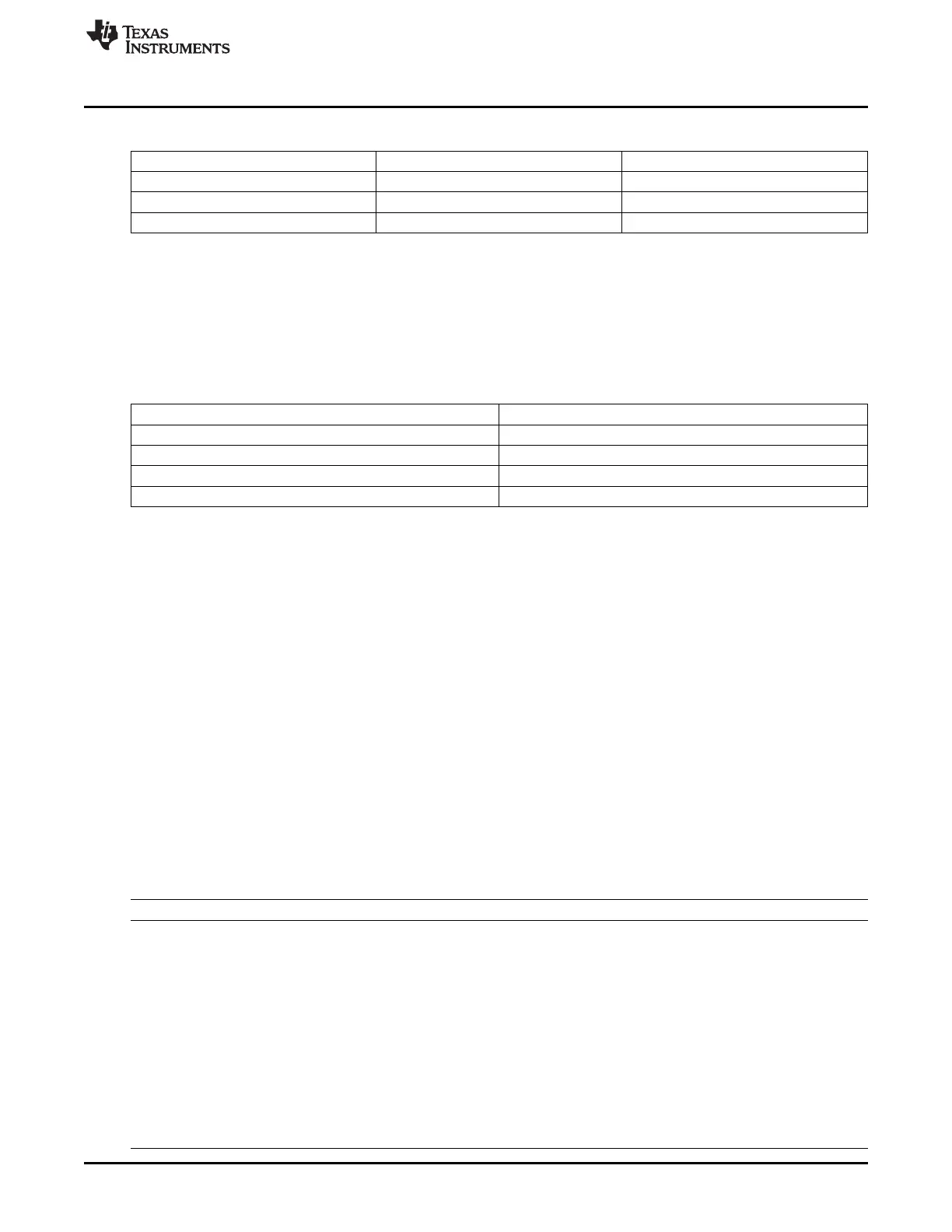

Table 20-33. Prescaler Clock Ratios Value (continued)

PRE PTV Divisor (PS)

1 5 64

1 6 128

1 7 256

The timer rate equation is as follows:

(0xFFFF FFFF – TLDR + 1) x timer Clock period x Clock Divider (PS)

With timer Clock period = 1/ timer Clock frequency and PS = 2(PTV + 1).

As example, if we consider a timer clock input of 32 KHz, with a PRE field equals to “0”, the timer output

period is:

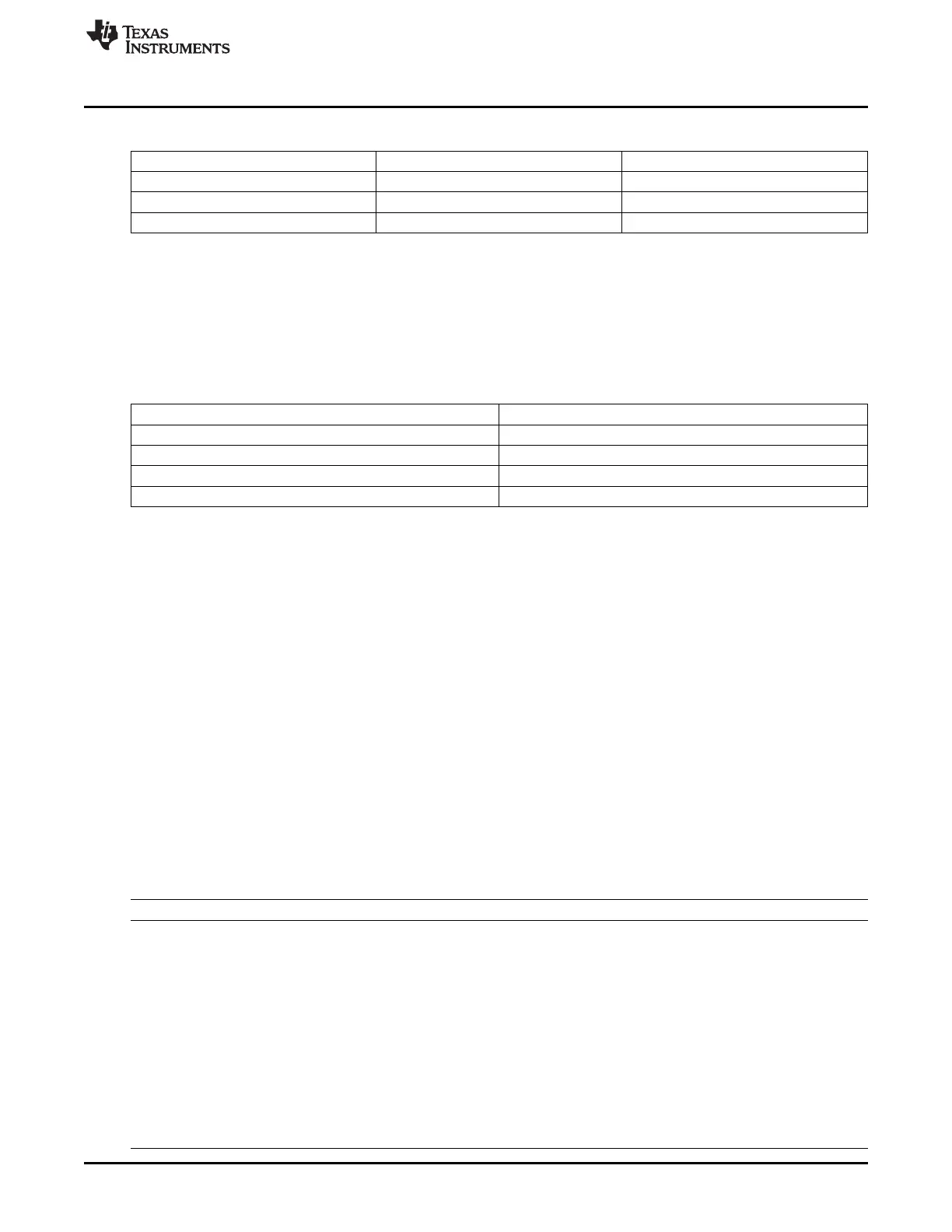

Table 20-34. Value and Corresponding Interrupt Period

TLDR Interrupt Period

0x0000 0000 37 h

0xFFFF 0000 2 s

0xFFFF FFF0 500 us

0xFFFF FFFE 62.5 us

20.2.3.9 Dual Mode Timer Under Emulation

During emulation mode (when PINSUSPENDN signal is active), the timer can/cannot continue running

according to the value of the EmuFree bit of the timer OCP configuration register (TIOCP_CFG).

If EmuFree is 1, timer execution is not stopped and, regardless of the value of PINSUSPENDN signal, and

the interrupt assertion is still generated when overflow is reached.

If EmuFree is 0, counters (prescaler/timer) are frozen and an increment start occurs again as soon as

PINSUSPENDN becomes inactive. The asynchronous input pin is internally synchronized on 2 TIMER

clock rising edges.

20.2.4 Use Cases

20.2.5 DMTIMER_1MS Registers

Table 20-35 lists the memory-mapped registers for the DMTIMER_1MS. All register offset addresses not

listed in Table 20-35 should be considered as reserved locations and the register contents should not be

modified.

Table 20-35. DMTIMER_1MS REGISTERS

Offset Acronym Register Name Section

0h TIDR This register contains the IP revision code Section 20.2.5.1

10h TIOCP_CFG This register controls the various parameters of the OCP Section 20.2.5.2

interface

14h TISTAT This register provides status information about the Section 20.2.5.3

module, excluding the interrupt status information

18h TISR The Timer Status Register is used to determine which of Section 20.2.5.4

the timer events requested an interrupt.

1Ch TIER This register controls (enable/disable) the interrupt Section 20.2.5.5

events

20h TWER This register controls (enable/disable) the wakeup Section 20.2.5.6

feature on specific interrupt events

24h TCLR This register controls optional features specific to the Section 20.2.5.7

timer functionality

3597

SPRUH73H–October 2011–Revised April 2013 Timers

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...