McASP Registers

www.ti.com

22.4.1.33 Transmitter Status Register (XSTAT)

The transmitter status register (XSTAT) provides the transmitter status and transmit TDM time slot

number. If the McASP logic attempts to set an interrupt flag in the same cycle that the CPU writes to the

flag to clear it, the McASP logic has priority and the flag remains set. This also causes a new interrupt

request to be generated. The XSTAT is shown in Figure 22-71 and described in Table 22-44.

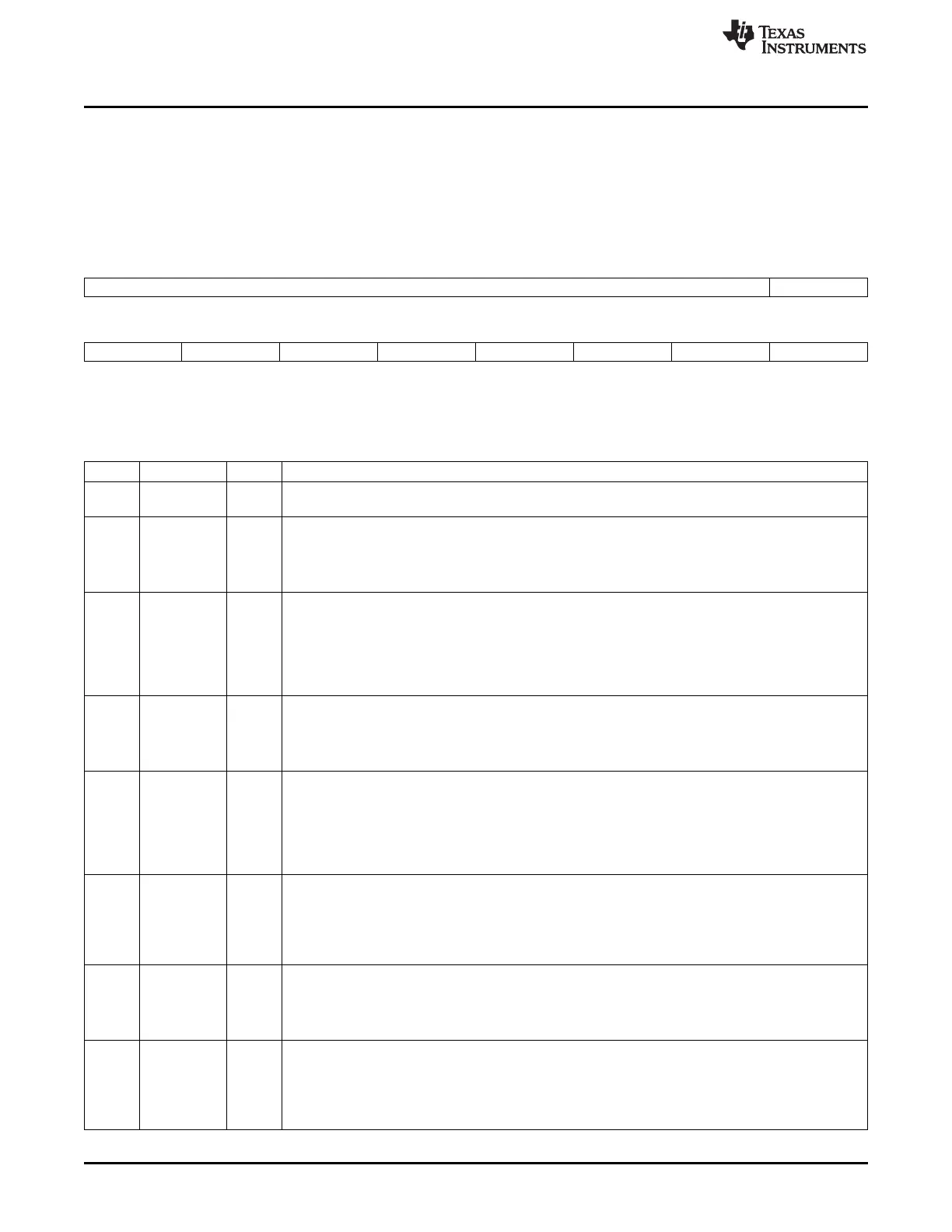

Figure 22-71. Transmitter Status Register (XSTAT)

31 9 8

Reserved XERR

R-0 R/W-0

7 6 5 4 3 2 1 0

XDMAERR XSTAFRM XDATA XLAST XTDMSLOT XCKFAIL XSYNCERR XUNDRN

R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R-0 R/W1C-0 R/W1C-0 R/W1C-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Writing a 1 clears this bit; writing a 0 has no effect; -n = value after reset

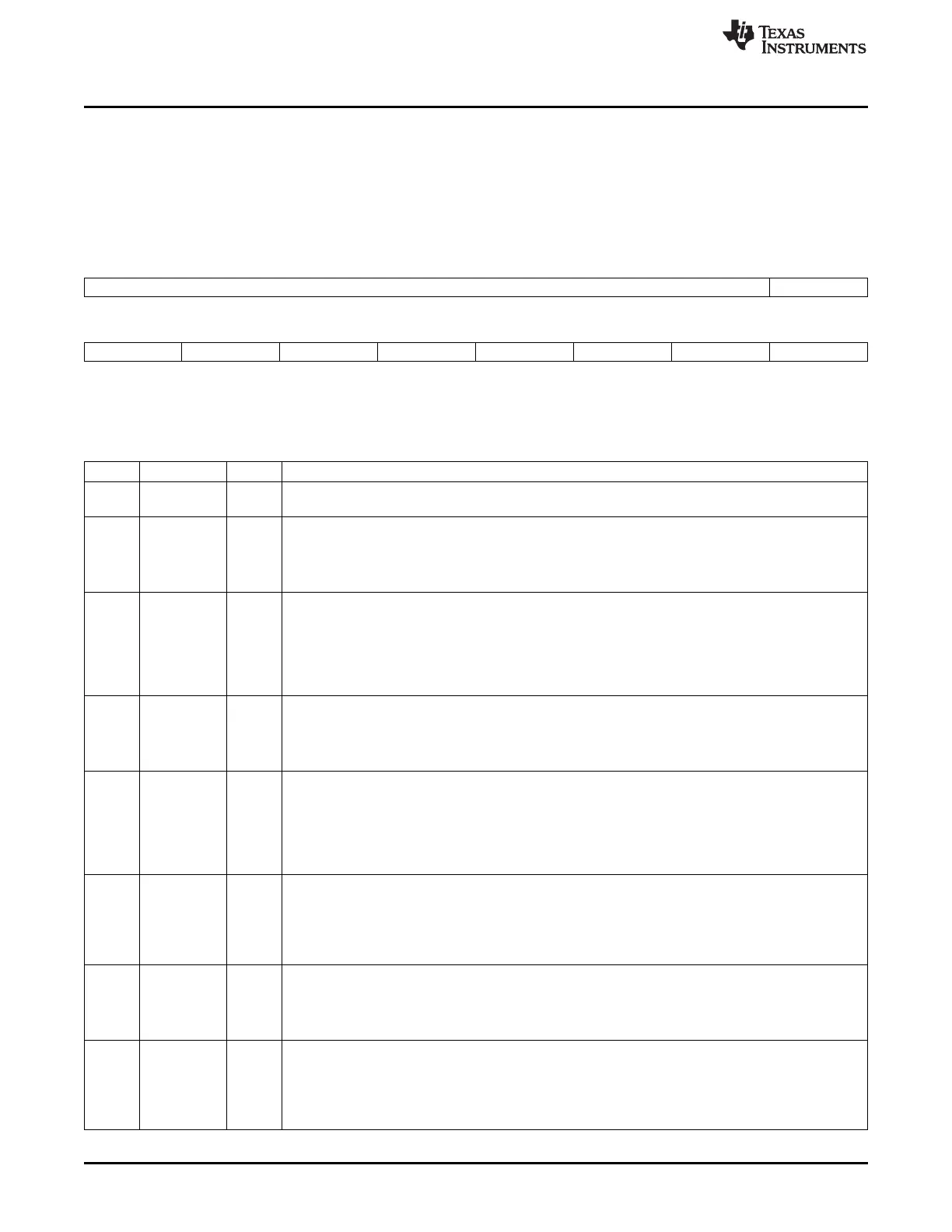

Table 22-44. Transmitter Status Register (XSTAT) Field Descriptions

Bit Field Value Description

31-9 Reserved 0 Reserved. The reserved bit location always returns the default value. A value written to this field has no

effect. If writing to this field, always write the default value for future device compatibility.

8 XERR XERR bit always returns a logic-OR of:XUNDRN | XSYNCERR | XCKFAIL | XDMAERR

Allows a single bit to be checked to determine if a transmitter error interrupt has occurred.

0 No errors have occurred.

1 An error has occurred.

7 XDMAERR Transmit DMA error flag. XDMAERR is set when the CPU or DMA writes more serializers through the

data port in a given time slot than were programmed as transmitters. Causes a transmit interrupt

(XINT), if this bit is set and XDMAERR in XINTCTL is set. This bit is cleared by writing a 1 to this bit.

Writing a 0 has no effect.

0 Transmit DMA error did not occur.

1 Transmit DMA error did occur.

6 XSTAFRM Transmit start of frame flag. Causes a transmit interrupt (XINT), if this bit is set and XSTAFRM in

XINTCTL is set. This bit is cleared by writing a 1 to this bit. Writing a 0 has no effect.

0 No new transmit frame sync (AFSX) is detected.

1 A new transmit frame sync (AFSX) is detected.

5 XDATA Transmit data ready flag. Causes a transmit interrupt (XINT), if this bit is set and XDATA in XINTCTL is

set. This bit is cleared by writing a 1 to this bit. Writing a 0 has no effect.

0 XBUF is written and is full.

1 Data is copied from XBUF to XRSR. XBUF is empty and ready to be written. XDATA is also set when

the transmit serializers are taken out of reset. When XDATA is set, it always causes a DMA event

(AXEVT).

4 XLAST Transmit last slot flag. XLAST is set along with XDATA, if the current slot is the last slot in a frame.

Causes a transmit interrupt (XINT), if this bit is set and XLAST in XINTCTL is set. This bit is cleared by

writing a 1 to this bit. Writing a 0 has no effect.

0 Current slot is not the last slot in a frame.

1 Current slot is the last slot in a frame. XDATA is also set.

3 XTDMSLOT Returns the LSB of XSLOT. Allows a single read of XSTAT to determine whether the current TDM time

slot is even or odd.

0 Current TDM time slot is odd.

1 Current TDM time slot is even.

2 XCKFAIL Transmit clock failure flag. XCKFAIL is set when the transmit clock failure detection circuit reports an

error (see Clock Failure Detection). Causes a transmit interrupt (XINT), if this bit is set and XCKFAIL in

XINTCTL is set. This bit is cleared by writing a 1 to this bit. Writing a 0 has no effect.

0 Transmit clock failure did not occur.

1 Transmit clock failure did occur.

3870

Multichannel Audio Serial Port (McASP) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...