Ethernet Subsystem Registers

www.ti.com

14.5.9.20 C0_MISC_STAT Register (offset = 4Ch) [reset = 0h]

C0_MISC_STAT is shown in Figure 14-216 and described in Table 14-234.

SUBSYSTEM CORE 0 MISC INTERRUPT MASKED INT STATUS REGISTER

Figure 14-216. C0_MISC_STAT Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved C0_MISC_STAT

R-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

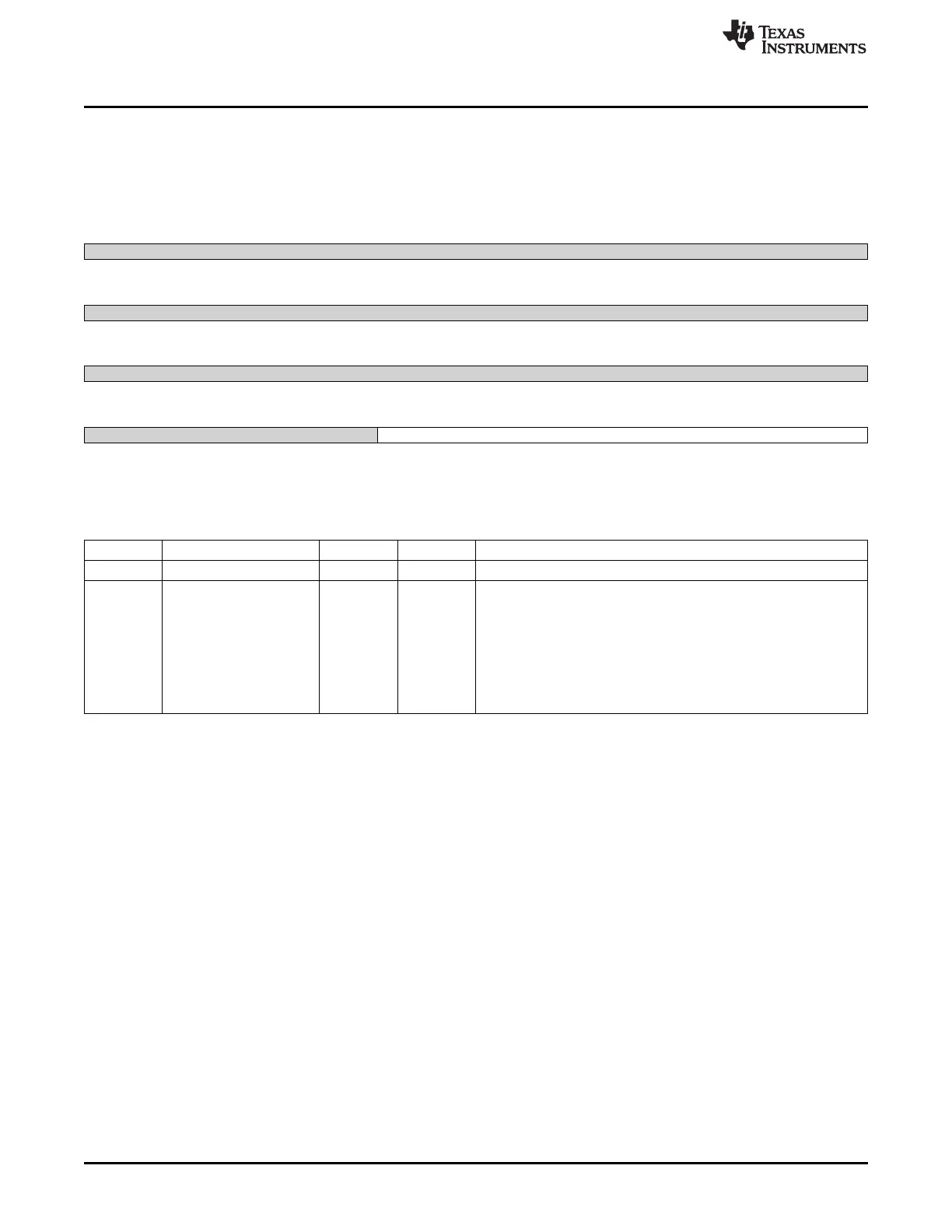

Table 14-234. C0_MISC_STAT Register Field Descriptions

Bit Field Type Reset Description

31-5 Reserved R 0h

4-0 C0_MISC_STAT R 0h Core 0 Misc Masked Interrupt Status - Each bit in this register

corresponds to the miscellaneous interrupt (evnt_pend, stat_pend,

host_pend, mdio_linkint, mdio_userint) that is enabled and

generating an interrupt on C0_MISC_PULSE.

Bit 4 = evnt_pend

Bit 3 = stat_pend

Bit 2 = host_pend

Bit 1 = mdio_linkint

Bit 0 = mdio_userint

1458

Ethernet Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...