Enhanced PWM (ePWM) Module

www.ti.com

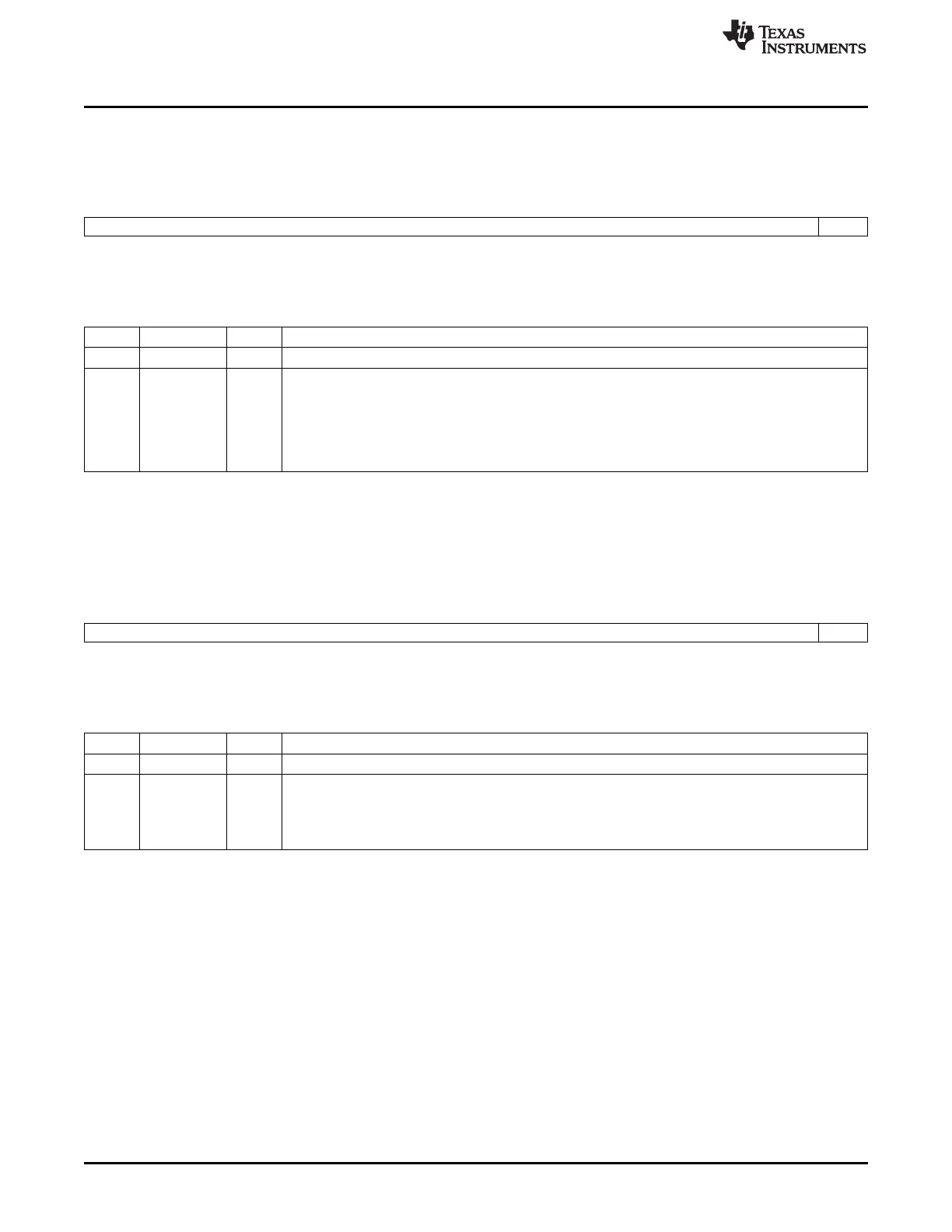

15.2.4.6.3 Event-Trigger Flag Register (ETFLG)

The event-trigger flag register (ETFLG) is shown in Figure 15-93 and described in Table 15-88.

Figure 15-93. Event-Trigger Flag Register (ETFLG)

15 1 0

Reserved INT

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 15-88. Event-Trigger Flag Register (ETFLG) Field Descriptions

Bits Name Value Description

15-1 Reserved 0 Reserved

0 INT Latched ePWM Interrupt (EPWMx_INT) Status Flag

0 Indicates no event occurred

1 Indicates that an ePWMx interrupt (EWPMx_INT) was generated. No further interrupts will be generated

until the flag bit is cleared. Up to one interrupt can be pending while the ETFLG[INT] bit is still set. If an

interrupt is pending, it will not be generated until after the ETFLG[INT] bit is cleared. Refer to Figure 15-

47.

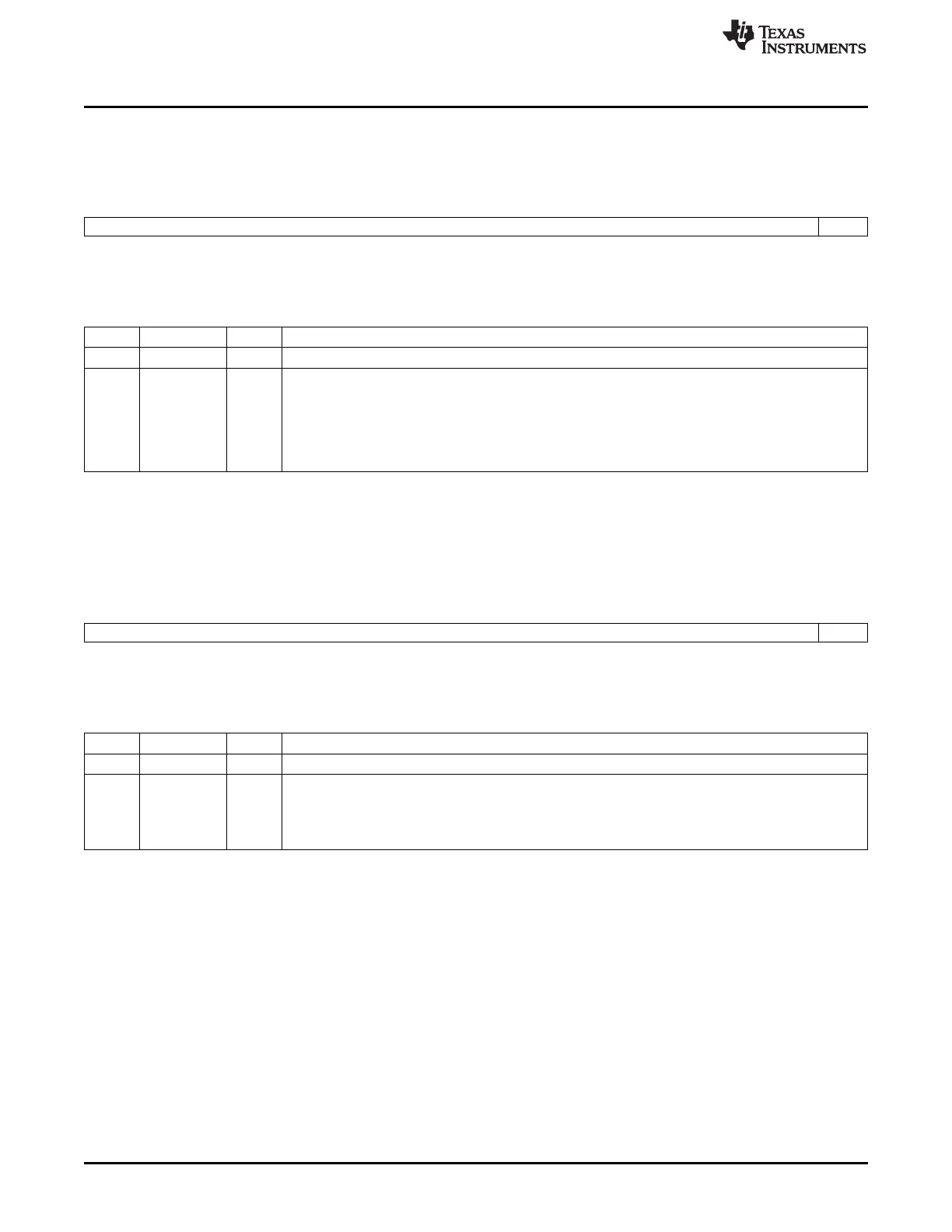

15.2.4.6.4 Event-Trigger Clear Register (ETCLR)

The event-trigger clear register (ETCLR) is shown in Figure 15-94 and described in Table 15-89.

Figure 15-94. Event-Trigger Clear Register (ETCLR)

15 1 0

Reserved INT

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 15-89. Event-Trigger Clear Register (ETCLR) Field Descriptions

Bits Name Value Description

15-1 Reserved 0 Reserved

0 INT ePWM Interrupt (EPWMx_INT) Flag Clear Bit

0 Writing a 0 has no effect. Always reads back a 0.

1 Clears the ETFLG[INT] flag bit and enable further interrupts pulses to be generated. Note that interrupts

can also used as DMA events, and this will also enable further DMA events to be generated.

1602

Pulse-Width Modulation Subsystem (PWMSS) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...