1/(N+1)

7 bits

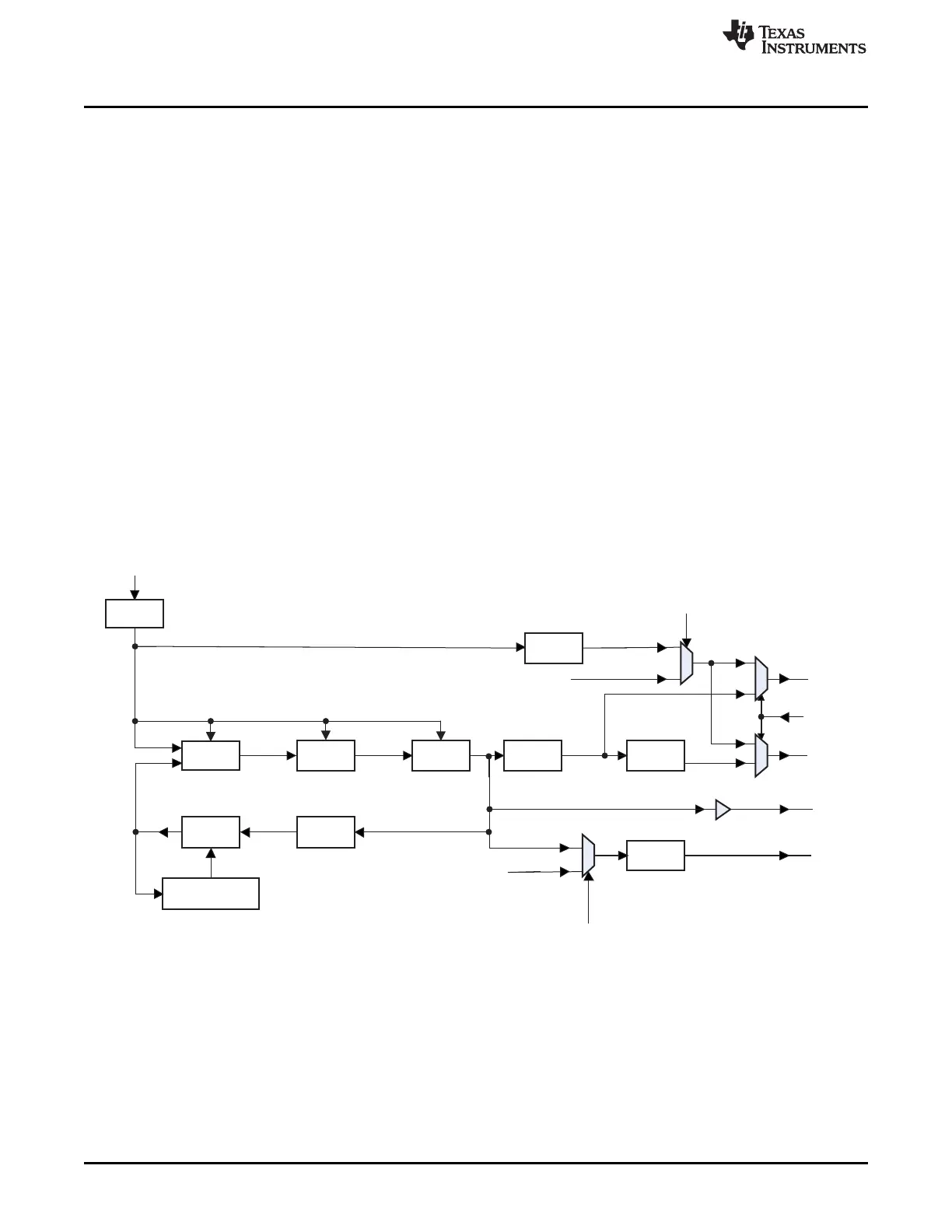

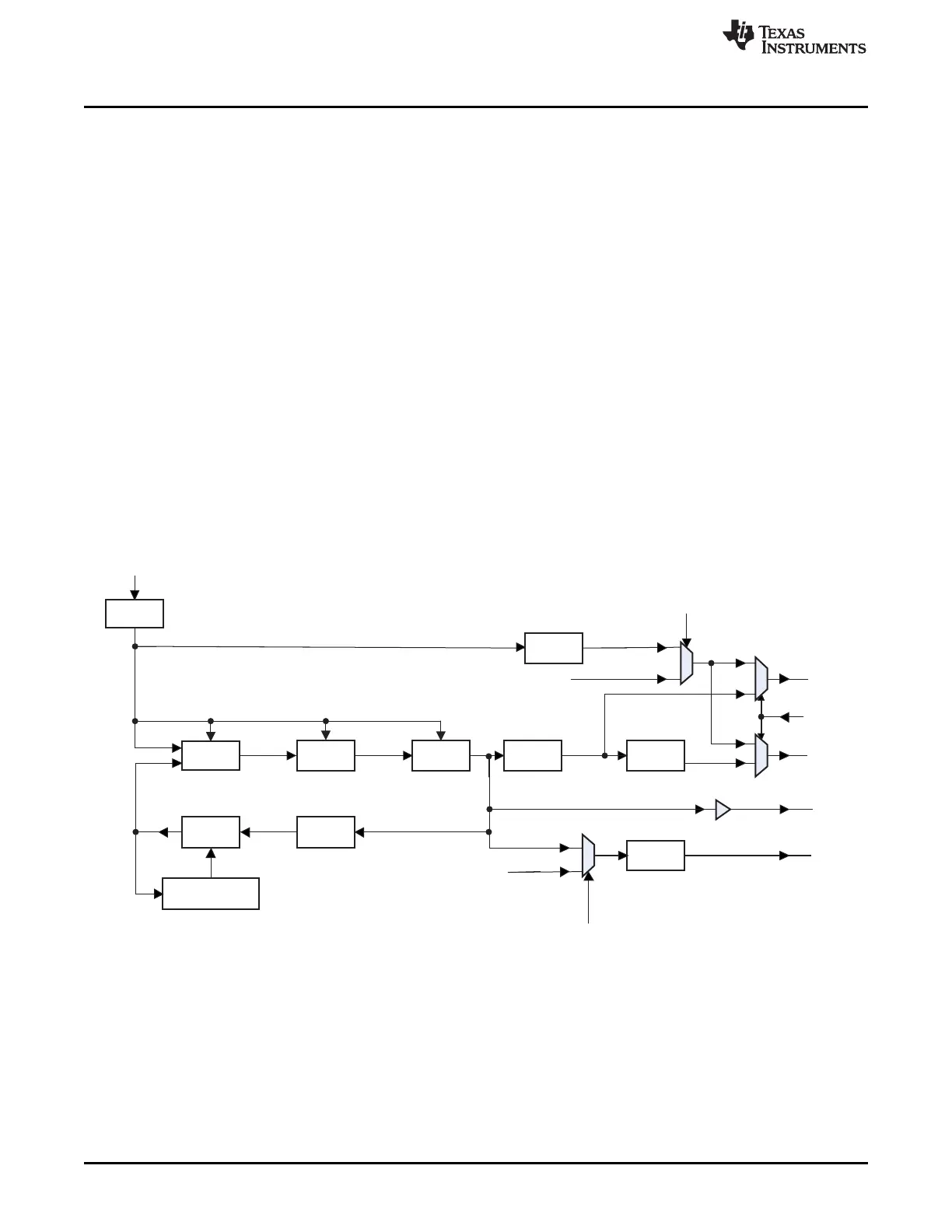

CLKINP

PFD

Multiplier

DAC

1/M2

(5 bits)

½

(1 bit)

½

(1 bit)

1/M.f

SSC sigmadelta

1/M3

(5 bits)

1/(N2+1)

(4 bits)

REFCLK

FBCLK

CLKINPULOW

ULOWCLKEN

CLKOUTX2

BYPASS_INT

CLKOUT

CLKDCOLDO

CLKOUTHIF

CLKINPHIFSEL

CLKINPHIF

Power, Reset, and Clock Management

www.ti.com

The device has two reference clocks which are generated by on-chip oscillators or externally. These are

for the main clock tree and RTC block, respectively.

In the case of an external oscillator, a clock can directly be connected to XTALIN pin and the oscillator will

be put in bypass mode. The 32-Khz crystal oscillator is controlled and configurable by RTC IP. This device

also contains an on-chip RC oscillator. This oscillator is not configurable and is always on.

The main oscillator on the device (see Chapter 26, Initialization, for possible frequencies) produces the

master high frequency clock CLK_M_OSC.

8.1.6.3 ADPLLS

The ADPLLS is a high resolution frequency synthesizer PLL with built in level shifters which allows the

generation of PLL locked frequencies up to 2 GHz. ADPLLS has a predivide feature which allows user to

divide, for instance, a 24- or 26-MHz reference clock to 1-MHz and then multiply up to 2-GHz maximum.

All PLLs will come-up in bypass mode at reset. SW needs to program all the PLL settings appropriately

and then wait for PLL to be locked. For more details, see the configuration procedure for each PLL.

The following PLLs are:

• MPU PLL

• Core PLL

• Display PLL

• DDR PLL

Figure 8-8. ADPLLS

The ADPLLS has three input clocks:

• CLKINP: Reference input clock

• CLKINPULOW: Low frequency input clock for bypass mode only.

• CLKINPHIF: High Frequency Input Clock for post-divider M3

The ADPLLS has four output clocks:

• CLKOUTHIF: High Frequency Output Clock from Post divider M3

• CLKOUTX2: Secondary 2x Output

• CLKOUT: Primary output clock

• CLKDCOLDO: Oscillator (DCO) output clock with no bypass

520

Power, Reset, and Clock Management (PRCM) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...