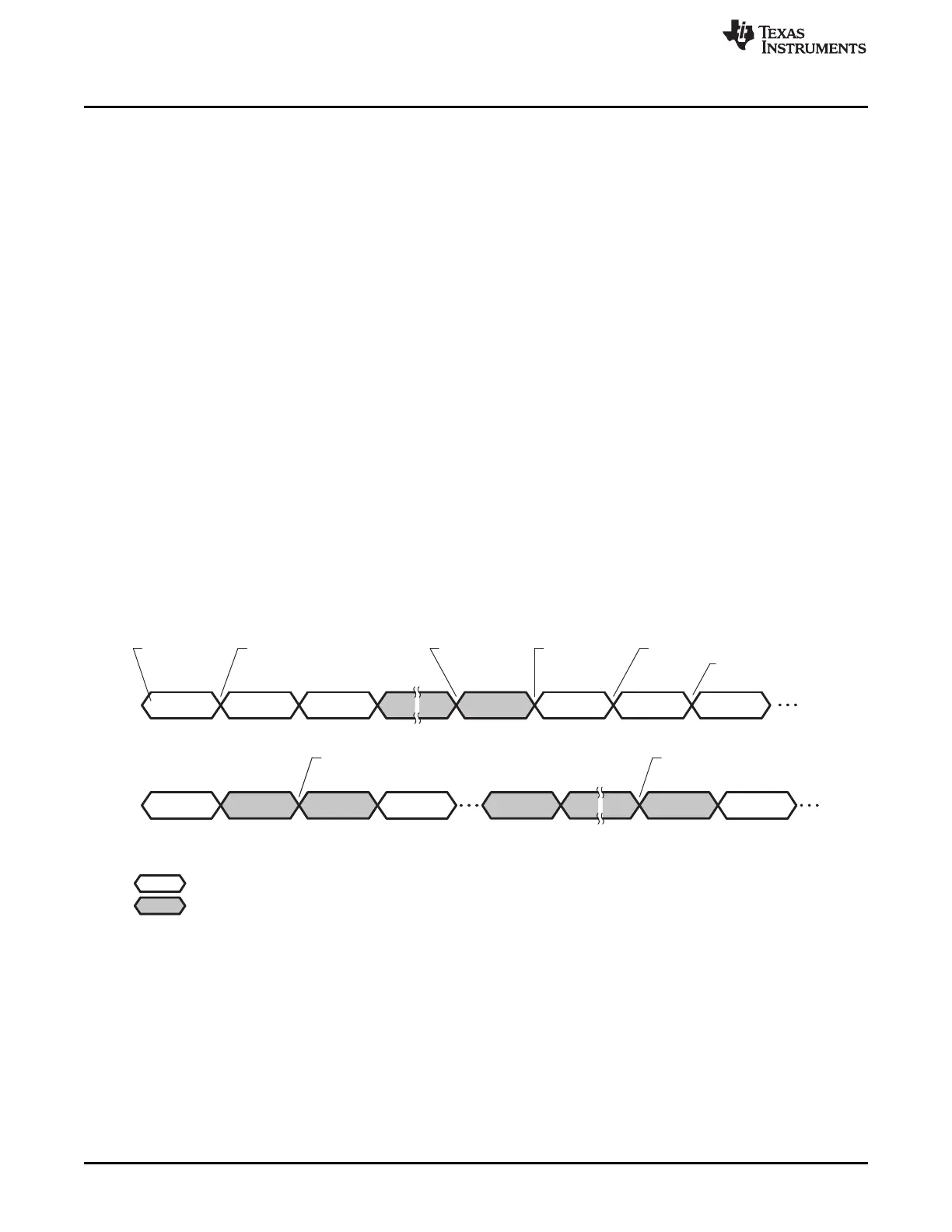

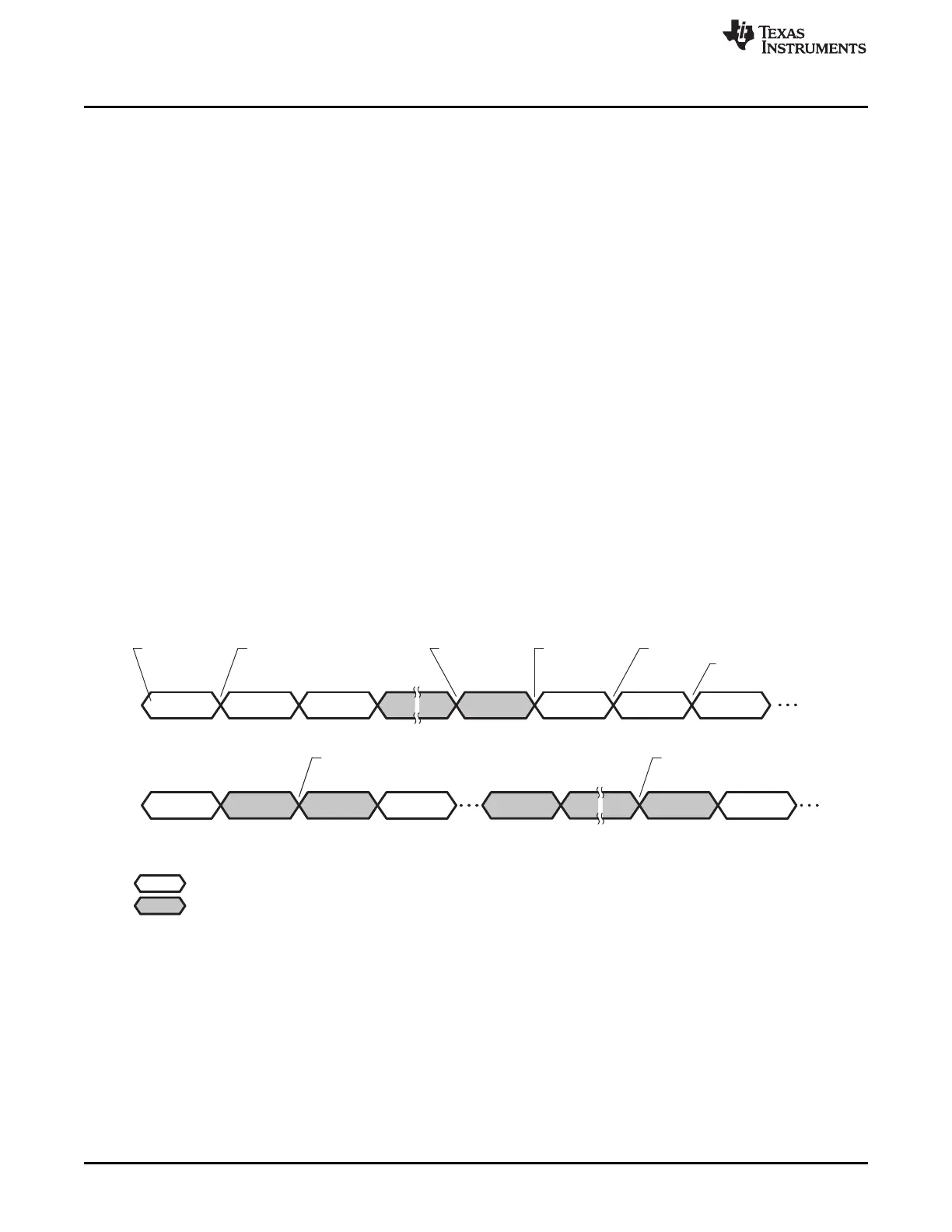

Slot 1Slot 0 Slot N−1

Slot M

Slot N+1

EDMA event

for slot 0

EDMA event

for slot 1

EDMA event

for slot N − 1

EDMA event

for slot N

EDMA event

for slot N + 1

Slot 1 Slot 2 Slot N

Slot N

EDMA event

for slot 2

EDMA event

for slot M

Active slot

Inactive slot

Slot N−2

Slot 0 Slot M−1

Initialization

period

(A)

EDMA event

for slot N + 2

Initialization

period

(A)

Functional Description

www.ti.com

22.3.8.2.1 TDM Time Slots

TDM mode on the McASP can extend to support multiprocessor applications, with up to 32 time slots per

frame. For each of the time slots, the McASP may be configured to participate or to be inactive by

configuring XTDM and/or RTDM (this allows multiple processors to communicate on the same TDM serial

bus).

The TDM sequencer (separate ones for transmit and receive) functions in this mode. The TDM sequencer

counts the slots beginning with the frame sync. For each slot, the TDM sequencer checks the respective

bit in either XTDM or RTDM to determine if the McASP should transmit/receive in that time slot.

If the transmit/receive bit is active, the McASP functions normally during that time slot; otherwise, the

McASP is inactive during that time slot; no update to the buffer occurs, and no event is generated.

Transmit pins are automatically set to a high-impedance state, 0, or 1 during that slot, as determined by

bit DISMOD in SRCTL[n].

Figure 22-21 shows when the transmit DMA event AXEVT is generated. See Section 22.3.10.1.1 for

details on data ready and the initialization period indication. The transmit DMA event for an active time slot

(slot N) is generated during the previous time slot (slot N - 1), regardless if the previous time slot (slot N -

1) is active or inactive.

During an active transmit time slot (slot N), if the next time slot (slot N + 1) is configured to be active, the

copy from XRBUF[n] to XRSR[n] generates the DMA event for time slot N + 1. If the next time slot (slot

N + 1) is configured to be inactive, then the DMA event will be delayed to time slot M - 1. In this case, slot

M is the next active time slot. The DMA event for time slot M is generated during the first bit time of slot

M - 1.

The receive DMA request generation does not need this capability, since the receive DMA event is

generated after data is received in the buffer (looks back in time). If a time slot is disabled, then no data is

copied to the buffer for that time slot and no DMA event is generated.

Figure 22-21. Transmit DMA Event (AXEVT) Generation in TDM Time Slots

A See Section 22.3.12.2, step 7a.

3790

Multichannel Audio Serial Port (McASP) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...