www.ti.com

Enhanced PWM (ePWM) Module

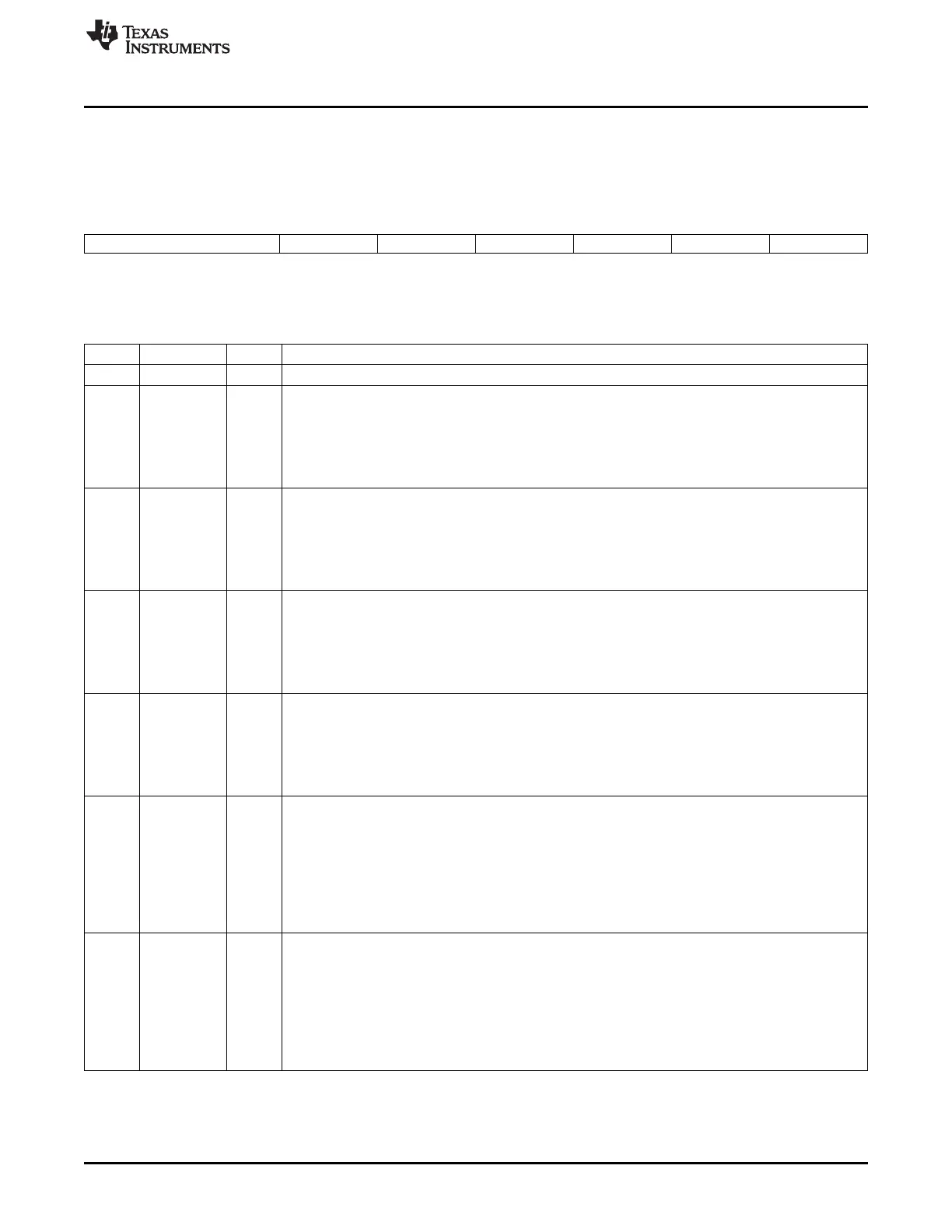

15.2.4.3.2 Action-Qualifier Output B Control Register (AQCTLB)

The action-qualifier output B control register (AQCTLB) is shown in Figure 15-79 and described in

Table 15-71.

Figure 15-79. Action-Qualifier Output B Control Register (AQCTLB)

15 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved CBD CBU CAD CAU PRD ZRO

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

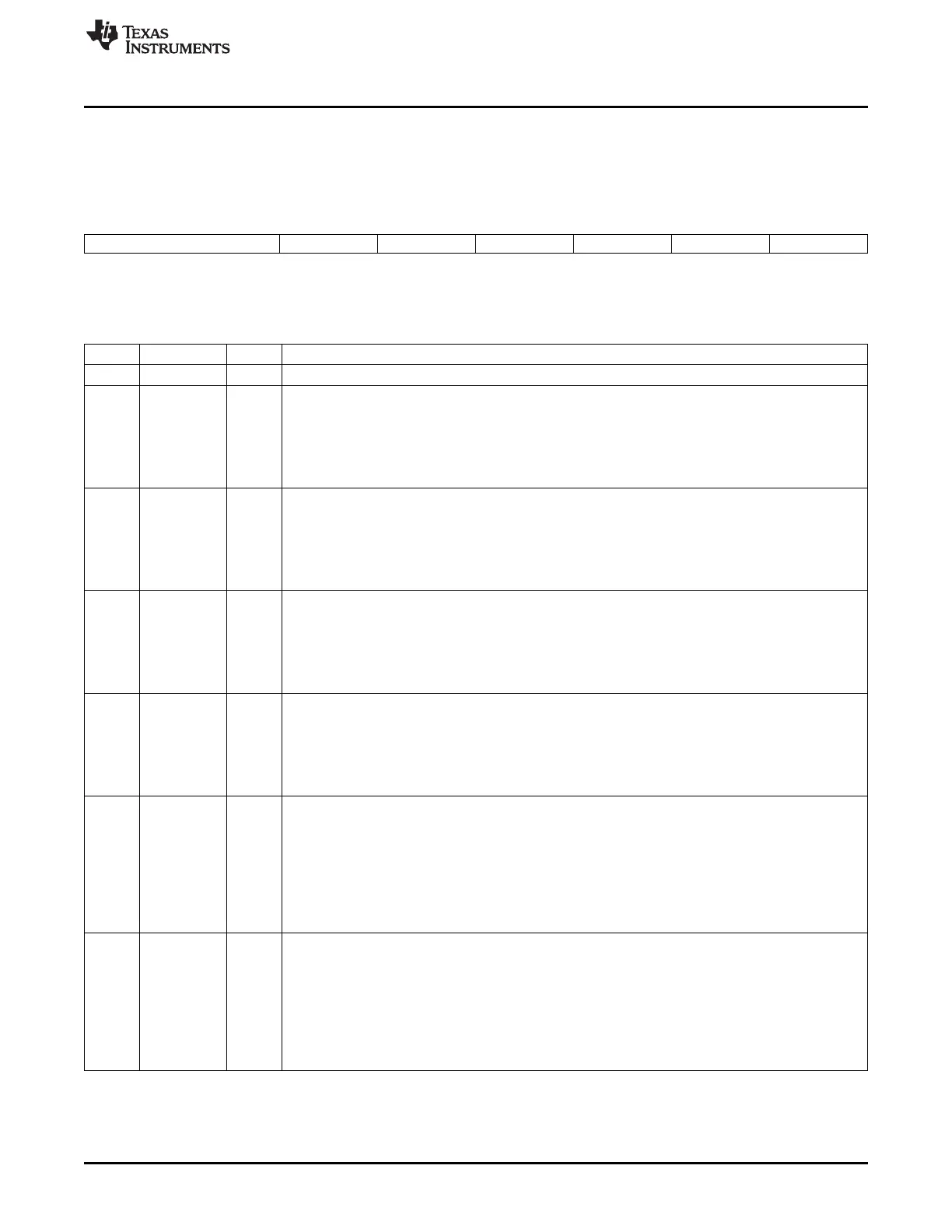

Table 15-71. Action-Qualifier Output B Control Register (AQCTLB) Field Descriptions

Bits Name Value Description

15-12 Reserved 0 Reserved

11-10 CBD 0-3h Action when the counter equals the active CMPB register and the counter is decrementing.

0 Do nothing (action disabled)

1h Clear: force EPWMxB output low.

2h Set: force EPWMxB output high.

3h Toggle EPWMxB output: low output signal will be forced high, and a high signal will be forced low.

9-8 CBU 0-3h Action when the counter equals the active CMPB register and the counter is incrementing.

0 Do nothing (action disabled)

1h Clear: force EPWMxB output low.

2h Set: force EPWMxB output high.

3h Toggle EPWMxB output: low output signal will be forced high, and a high signal will be forced low.

7-6 CAD 0-3h Action when the counter equals the active CMPA register and the counter is decrementing.

0 Do nothing (action disabled)

1h Clear: force EPWMxB output low.

2h Set: force EPWMxB output high.

3h Toggle EPWMxB output: low output signal will be forced high, and a high signal will be forced low.

5-4 CAU 0-3h Action when the counter equals the active CMPA register and the counter is incrementing.

0 Do nothing (action disabled)

1h Clear: force EPWMxB output low.

2h Set: force EPWMxB output high.

3h Toggle EPWMxB output: low output signal will be forced high, and a high signal will be forced low.

3-2 PRD 0-3h Action when the counter equals the period.

Note: By definition, in count up-down mode when the counter equals period the direction is defined as 0

or counting down.

0 Do nothing (action disabled)

1h Clear: force EPWMxB output low.

2h Set: force EPWMxB output high.

3h Toggle EPWMxB output: low output signal will be forced high, and a high signal will be forced low.

1-0 ZRO 0-3h Action when counter equals zero.

Note: By definition, in count up-down mode when the counter equals 0 the direction is defined as 1 or

counting up.

0 Do nothing (action disabled)

1h Clear: force EPWMxB output low.

2h Set: force EPWMxB output high.

3h Toggle EPWMxB output: low output signal will be forced high, and a high signal will be forced low.

1591

SPRUH73H–October 2011–Revised April 2013 Pulse-Width Modulation Subsystem (PWMSS)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...