www.ti.com

McASP Registers

22.4.1.44 Write FIFO Control Register (WFIFOCTL)

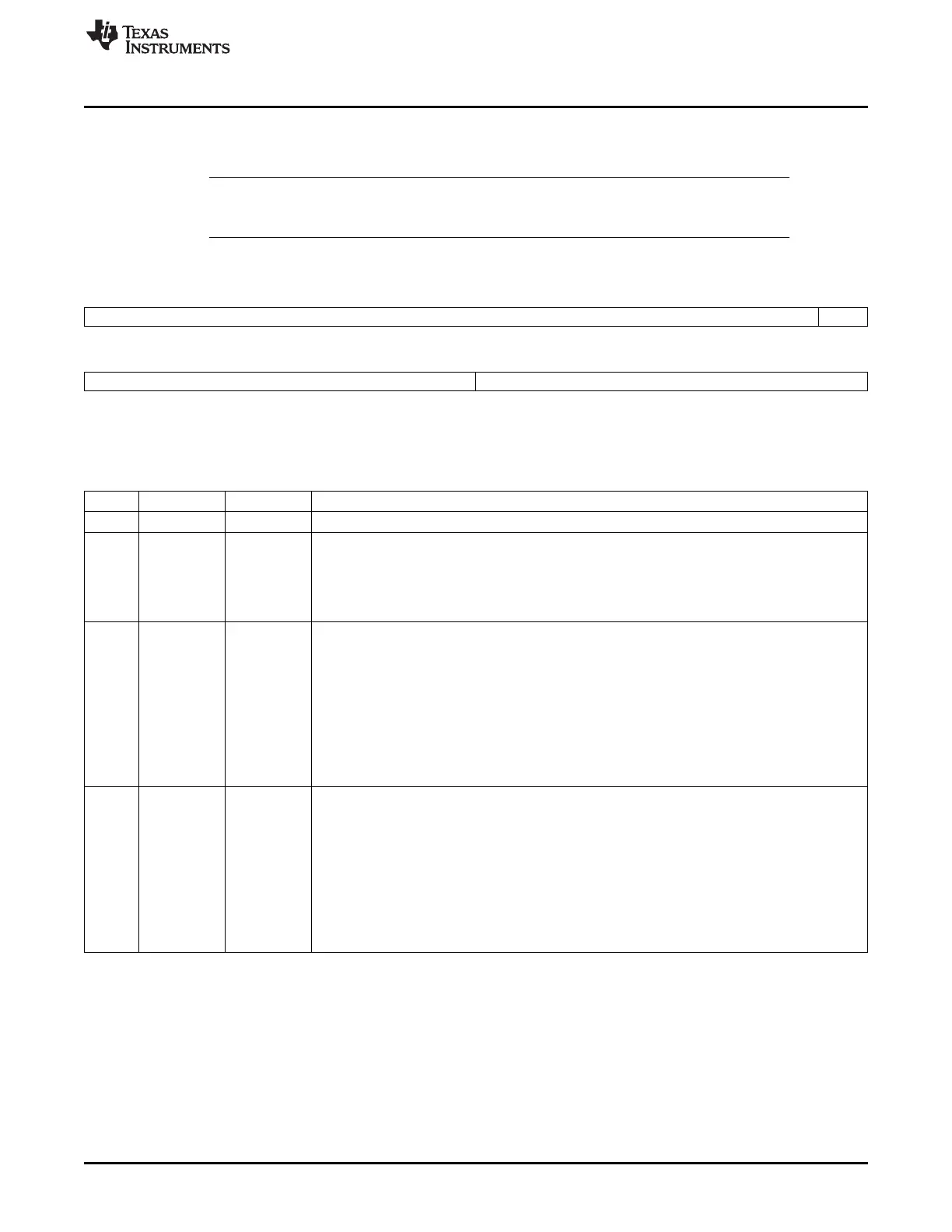

The Write FIFO control register (WFIFOCTL) is shown in Figure 22-82 and described in Table 22-49.

NOTE: The WNUMEVT and WNUMDMA values must be set prior to enabling the Write FIFO.

If the Write FIFO is to be enabled, it must be enabled prior to taking the McASP out of reset.

Figure 22-82. Write FIFO Control Register (WFIFOCTL)

31 17 16

Reserved WENA

R-0 R/W-0

15 8 7 0

WNUMEVT WNUMDMA

R/W-10h R/W-4h

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

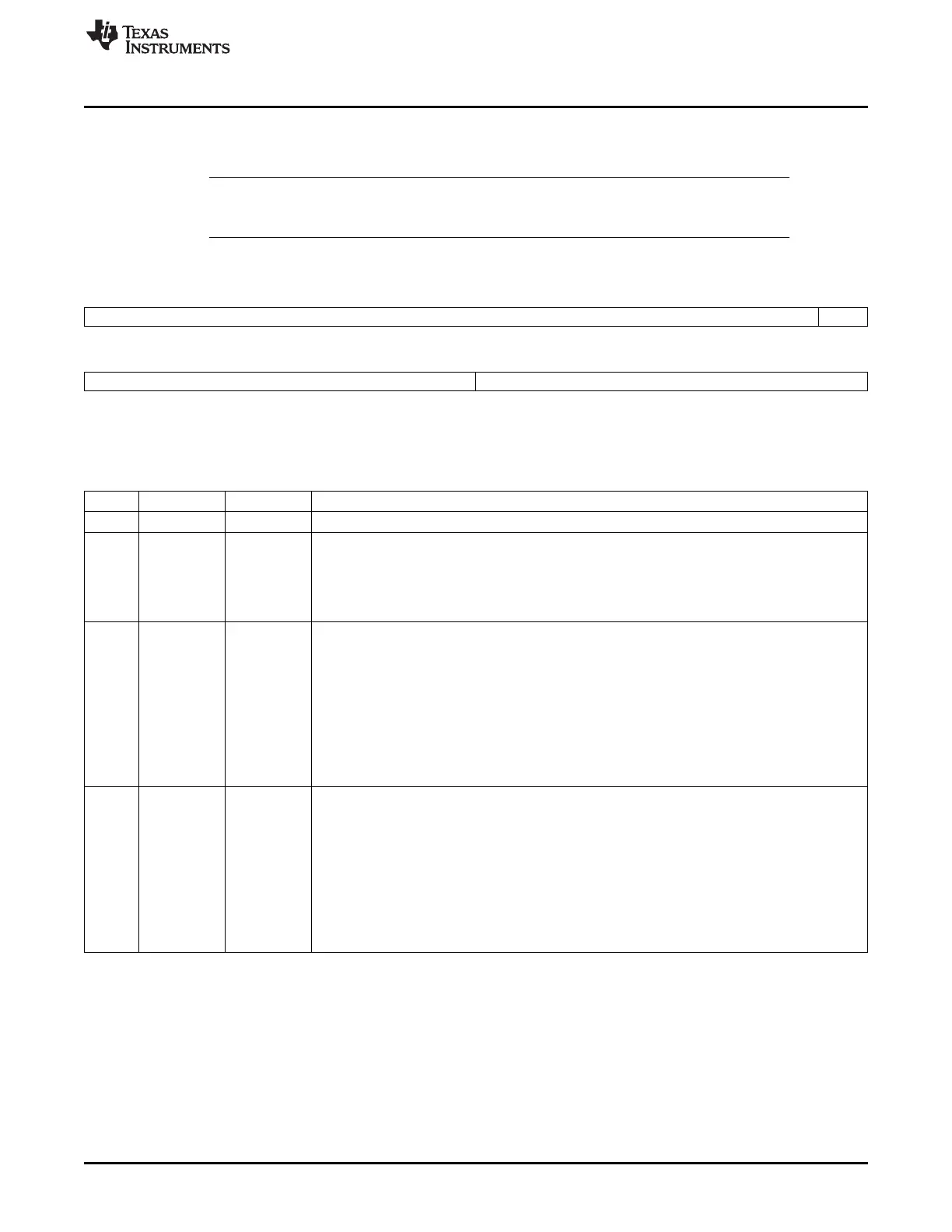

Table 22-49. Write FIFO Control Register (WFIFOCTL) Field Descriptions

Bit Field Value Description

31-17 Reserved 0 Reserved

16 WENA Write FIFO enable bit.

0 Write FIFO is disabled. The WLVL bit in the Write FIFO status register (WFIFOSTS) is reset to 0

and pointers are initialized, that is, the Write FIFO is “flushed.”

1 Write FIFO is enabled. If Write FIFO is to be enabled, it must be enabled prior to taking McASP

out of reset.

15-8 WNUMEVT 0-FFh Write word count per DMA event (32-bit). When the Write FIFO has space for at least WNUMEVT

words of data, then an AXEVT (transmit DMA event) is generated to the host/DMA controller. This

value should be set to a non-zero integer multiple of the number of serializers enabled as

transmitters. This value must be set prior to enabling the Write FIFO.

0 0 words

1h 1 word

2h 2 words

3h-40h 3 to 64 words

41h-FFh Reserved

7-0 WNUMDMA 0-FFh Write word count per transfer (32-bit words). Upon a transmit DMA event from the McASP,

WNUMDMA words are transferred from the Write FIFO to the McASP. This value must equal the

number of McASP serializers used as transmitters. This value must be set prior to enabling the

Write FIFO.

0 0 words

1h 1 word

2h 2 words

3h-10h 3-16 words

11h-FFh Reserved

3877

SPRUH73H–October 2011–Revised April 2013 Multichannel Audio Serial Port (McASP)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...