CONTROL_MODULE Registers

www.ti.com

9.3.76 dpll_pwr_sw_ctrl Register (offset = 1318h) [reset = 0h]

The DPLL_PWR_SW_CTRL register, in conjunction with the DPLL_PWR_SW_STATUS register, can be

used to power off the digital power domain of the 3 DPLLS – DDR, DISP, PER to save leakage power in

deep-sleep power modes. This register gives control over the power switch signals of the individual

DPLLS.

A specific sequence has to be followed while programming the RET, PONIN, PGOODIN, ISO and RESET

signals to put the PLLs in to low power mode and bring it out of low power mode.

In normal operating mode, the PRCM controls the RESET of the DPLLS. The RET, PONIN, PGOODIN

and ISO are tied off. An over-ride bit is provided in this register SW_CTRL_*_RESET, which when set

allows S/W to control the RESET, RET, PONIN, PGOODIN and ISO of the DPLLs to enable entry/exit into

DPLL low power modes.

dpll_pwr_sw_ctrl is shown in Figure 9-79 and described in Table 9-86.

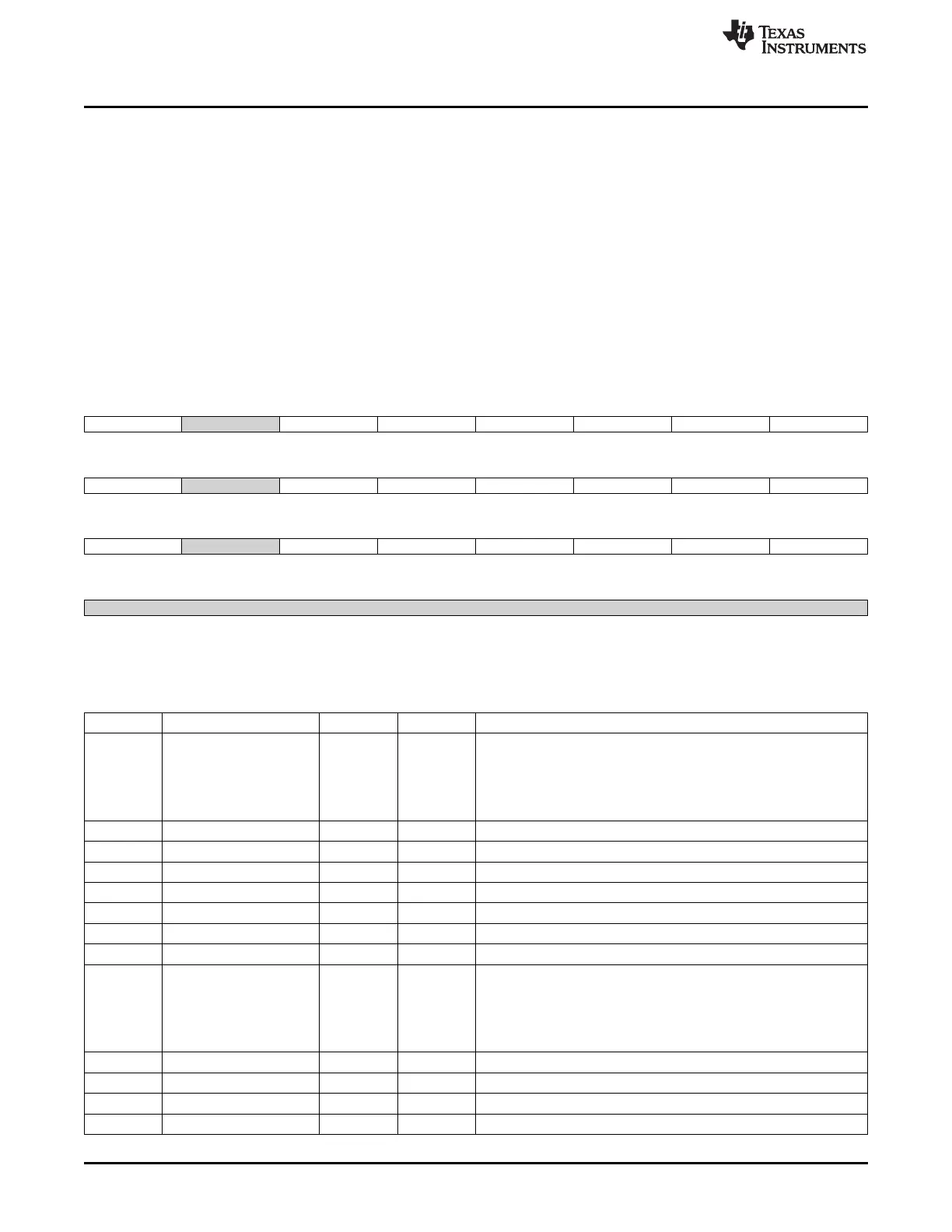

Figure 9-79. dpll_pwr_sw_ctrl Register

31 30 29 28 27 26 25 24

sw_ctrl_ddr_pll Reserved isoscan_ddr ret_ddr reset_ddr iso_ddr pgoodin_ddr ponin_ddr

R-0h R-0h R-0h R-0h R-0h R-0h R-1h R-1h

23 22 21 20 19 18 17 16

sw_ctrl_disp_pll Reserved isoscan_disp ret_disp reset_disp iso_disp pgoodin_disp ponin_disp

R-0h R-0h R-0h R-0h R-0h R-0h R-1h R-1h

15 14 13 12 11 10 9 8

sw_ctrl_per_dpll Reserved isoscan_per ret_per reset_per iso_per pgoodin_per ponin_per

R-0h R-0h R-0h R-0h R-0h R-0h R-1h R-1h

7 6 5 4 3 2 1 0

Reserved

R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

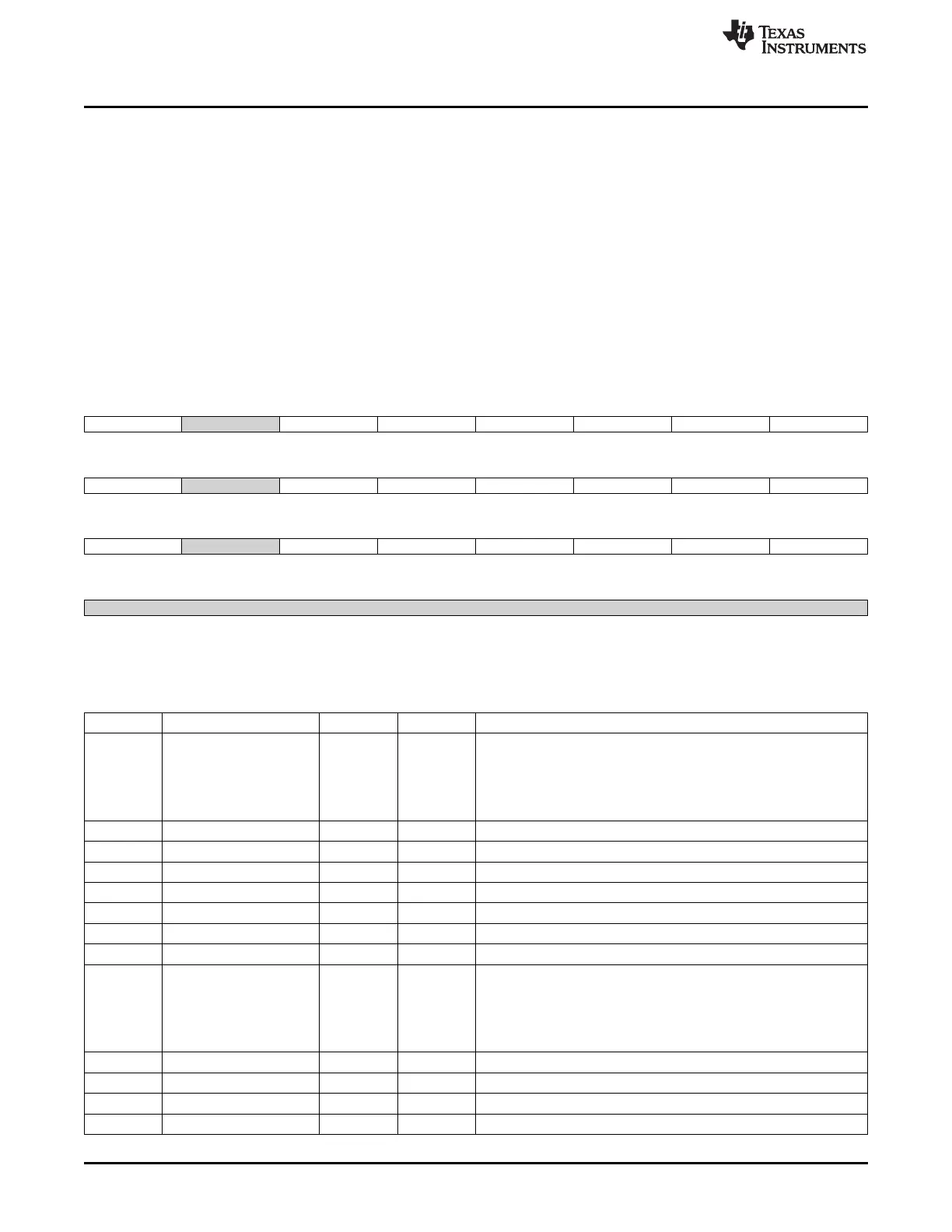

Table 9-86. dpll_pwr_sw_ctrl Register Field Descriptions

Bit Field Type Reset Description

31 sw_ctrl_ddr_pll R/W 0h

Enable software control over DDR DPLL RET, RESET, ISO,

PGOODIN, PONIN for power savings.

0: PRCM controls the DPLL reset, RET = 0, ISO = 0, PGOODIN = 1,

PONIN = 1.

1: Controlled by corresponding bits in this register.

30 Reserved R 0h

29 isoscan_ddr R/W 0h Drives ISOSCAN of DDR PLL.

28 ret_ddr R/W 0h Drives RET signal of DDR PLL.

27 reset_ddr R/W 0h Drives RESET of DDR DPLL.

26 iso_ddr R/W 0h Drives ISO of DDR DPLL.

25 pgoodin_ddr R/W 1h Drives PGOODIN of DDR DPLL.

24 ponin_ddr R/W 1h Drives PONIN of DDR DPLL.

23 sw_ctrl_disp_pll R/W 0h

Enable software control over DISP DPLL RET, RESET, ISO,

PGOODIN, PONIN for power savings.

0: PRCM controls the DPLL reset, RET = 0, ISO = 0, PGOODIN = 1,

PONIN = 1.

1: Controlled by corresponding bits in this register.

22 Reserved R 0h

21 isoscan_disp R/W 0h Drives ISOSCAN of DISP PLL.

20 ret_disp R/W 0h Drives RET of DISP DPLL.

19 reset_disp R/W 0h Drives RESET of DISP DPLL.

840

Control Module SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...